# Arbitrary Precision and Low Complexity Micro-Architectural Arithmetic Optimisations of Machine Learning Algorithms for Compute Bound and High-Performance Systems

by James Philip Garland

Submitted for the degree of Doctor of Philosophy (Computer Science)

School of Computer Science and Statistics

THE UNIVERSITY OF DUBLIN, TRINITY COLLEGE DUBLIN

2021

## Declaration

I declare that this thesis has not been submitted as an exercise for a degree at this or any other university and it is entirely my own work.

Alas land

I DI:1: C 1 1

James Philip Garland

Dated: 2021

### Permission to Lend and/or Copy

I agree to deposit this thesis in the University's open access institutional repository or allow the Library to do so on my behalf, subject to Irish Copyright Legislation and Trinity College Library conditions of use and acknowledgement.

I consent to the examiner retaining a copy of the thesis beyond the examining period, should they so wish (EU GDPR May 2018).

Aland S

.....

James Philip Garland

Dated: 2021

To my wife, Michelle,

my son, Toby and

my daughter, Zara,

without whom this thesis would have

probably been completed a year earlier ©

I love you!

iii

By the year 2600, the world's population would be standing shoulder to shoulder, and the electricity consumption would make the Earth glow red-hot.

Stephen Hawking, Tencent WE Summit, 2017

#### **Abstract**

ARTIFICIAL INTELLIGENCE is becoming ubiquitous and pervasive in our daily lives. *Machine learning (ML)*, a subset of *Artificial intelligence (AI)*, supplies more accurate internet searches, voice recognition in home appliances, tagging people in photos, object detection in videos, and driver assistance systems in vehicles. *Convolutional neural networks (CNNs)*, a subset of ML, process these images, videos and sometimes audio data. Captured and preprocessed by embedded *internet of things (IoT)* devices, CNN data are often processed in internet data centres or on local PCs with high-performance processors and acceleration cards, due to CNNs enormous energy, bandwidth, and processing requirements. There is a need to move more of this CNN processing to IoT edge and embedded devices for low-power and potentially offline, processing.

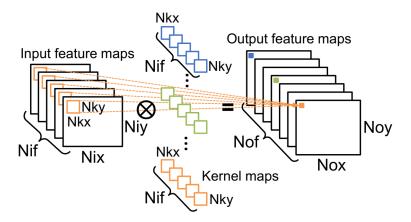

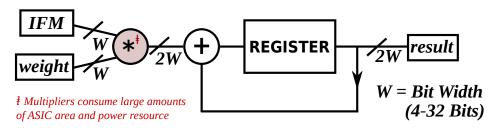

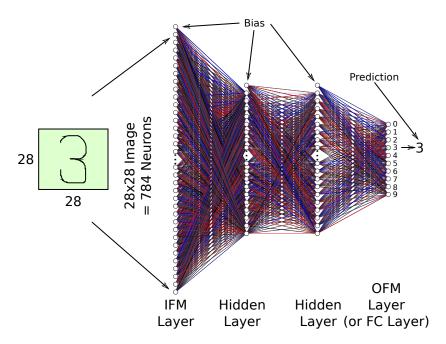

The CNN convolution layer consists of millions of multiply-accumulates (MACs), the arithmetic of which can be in fixed-point, integer or floating-point format. The CNN can operate in training mode or inference mode. During inference, the convolution layer occupies up to 90% of the computation time and energy of the CNN, convolving the input feature map (IFM) with the kernel weight data. The storage, movement of weight data, and acceleration of the convolution computation are often beyond the energy, storage and compute bounds of embedded devices.

We investigate opportunities for optimising the hardware energy efficiency, gatelevel area, and execution time of the CNN convolution layer's MAC arithmetic, while maintaining inference classification accuracy of the CNN accelerator implementation. Our first contribution investigates reducing energy consumption and application-specific integrated circuit (ASIC) die area while maintaining classification accuracy of CNNs. We also investigate latency and resource efficiency when implemented in field programmable gate array (FPGA). Our second contribution focuses on decreasing software execution time of low-precision floating-point (FP) CNNs by exploiting hardware optimisation of central processing unit (CPU) vector register packing and single instruction multiple data (SIMD) bitwise instructions used in the CNN MAC.

## Acknowledgements

My family: Michelle, Toby, and Zara, without whom I would have never attempted this PhD undertaking, let alone finish it. This PhD is just as much theirs as it is mine! They have had to do a lot to support me through this, for which I am forever grateful!

Dr David Gregg: The man, the professor, the legend! I always come away from meetings with David buzzing with new ideas or ways of tackling a research issue. I thoroughly enjoy working with David, bouncing wacky notions off whiteboards with him. David has always been incredibly supportive, giving guidance throughout and even working with me in the lab until 11 pm some nights. Best of all, he is a great laugh too, I mean, he still thinks I'm Australian (well, he is a stand-up comedian, and I have proof)!

Lab Mates: What a gang! Dr Andrew Anderson, Dr Aravind Vasudevan, Dr Shixiong Xu, Dr Yuan Wen, Dr Syed Asad Alam, Maria Francesca, Barbara (Basia) Barabasz, Kaveena Persand, Cormac Keane. It's been fun and productive, fostering new and innovative ideas for papers and writing a book chapter, discussing the mad politics of the world, moving labs, creating a new lab group identity in *Córais*, presenting to Science Foundation Ireland (SFI) and external professors, and more! I have loved every minute of it, and hope the collaboration continues! As Hebbian says, "cells that fire together wire together!"

**SFI & Institute of Technology Carlow**: This work was supported, in part, by Science Foundation Ireland grant 12/IA/1381. I extend an expression of thanks to the Institute of Technology Carlow, Carlow, Ireland, for their support.

**Mom & Dad**: Finally, I dedicate this to my parents, Cheryl and Jim. Wherever they are together on their continued journey in the universe, I would like to think they are proud! I love and miss you both!

JAMES GARLAND

Carlow, Ireland 31 March 2020

# Contents

| A | cronyms xvii |              |                                            |      |  |  |

|---|--------------|--------------|--------------------------------------------|------|--|--|

| G | lossa        | ossary       |                                            |      |  |  |

| 1 | Intr         | Introduction |                                            |      |  |  |

|   | 1.1          | Motiv        | vation                                     | . 2  |  |  |

|   | 1.2          | Objec        | tive and Approach                          | . 3  |  |  |

|   | 1.3          | Contr        | ributions                                  | . 3  |  |  |

|   | 1.4          | Thesis       | s Structure                                | . 4  |  |  |

|   | 1.5          | Public       | cations                                    | . 6  |  |  |

|   |              | 1.5.1        | Refereed Journals Articles                 | . 6  |  |  |

|   |              | 1.5.2        | Journal Article Submitted and Under Review | . 7  |  |  |

|   |              | 1.5.3        | Book Chapter Publications                  | . 7  |  |  |

|   | 1.6          | Journa       | al Articles Peer Reviewed                  | . 8  |  |  |

| 2 | Taxe         | onomy        | and Review of Neural Network Literature    | 9    |  |  |

|   | 2.1          | Introd       | duction                                    | . 9  |  |  |

|   | 2.2          | Archi        | tecture Optimisations                      | . 13 |  |  |

|   |              | 2.2.1        | Architecture Optimisation - Accuracy       | . 13 |  |  |

|   |              | 2.2.2        | Architecture Optimisation - Area           | . 14 |  |  |

|   |              | 2.2.3        | Architecture Optimisation - Energy         | . 15 |  |  |

|   |              | 2.2.4        | Architecture Optimisation - Execution Time | . 18 |  |  |

|   |              | 2.2.5        | Architecture Optimisation - Storage        | . 22 |  |  |

|   | 2.3 | Algor   | ithm Optimisation                                      | 23 |

|---|-----|---------|--------------------------------------------------------|----|

|   |     | 2.3.1   | Algorithmic Optimisation - Accuracy                    | 23 |

|   |     | 2.3.2   | Algorithmic Optimisation - Area                        | 25 |

|   |     | 2.3.3   | Algorithmic Optimisation - Energy                      | 26 |

|   |     | 2.3.4   | Algorithmic Optimisation - Execution Time              | 27 |

|   |     | 2.3.5   | Algorithmic Optimisation - Storage                     | 31 |

|   | 2.4 | Custo   | mising Bit-Precision                                   | 32 |

|   |     | 2.4.1   | Bit-Precision Optimisation - Accuracy                  | 32 |

|   |     | 2.4.2   | Bit-Precision Optimisation - Area                      | 33 |

|   |     | 2.4.3   | Bit-Precision Optimisation - Energy                    | 33 |

|   |     | 2.4.4   | Bit-Precision Optimisation - Execution Time            | 34 |

|   |     | 2.4.5   | Bit-Precision Optimisation - Storage                   | 36 |

|   | 2.5 | Concl   | usion                                                  | 37 |

|   | 2.6 | Centra  | al Tenets of this Research                             | 38 |

| _ | _   |         |                                                        |    |

| 3 |     | -       | elexity MAC Units for CNNs with Weight Sharing         | 41 |

|   | 3.1 |         | luction                                                | 41 |

|   | 3.2 |         | Convolution with Dictionary-Encoded Weights            | 42 |

|   |     | 3.2.1   | CNN Accelerators                                       | 42 |

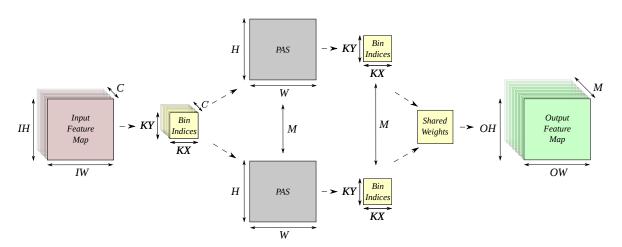

|   |     | 3.2.2   | The PASM Concept                                       | 46 |

|   |     | 3.2.3   | PASM accelerator                                       | 48 |

|   |     | 3.2.4   | Evaluation of PASM as a Stand-alone Unit               | 49 |

|   | 3.3 | PASM    | I in a CNN Accelerator                                 | 51 |

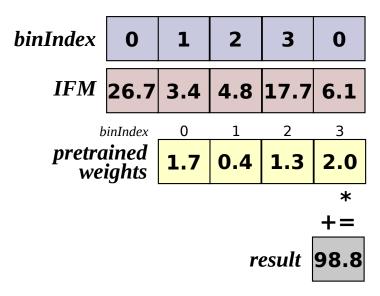

|   |     | 3.3.1   | Examples                                               | 53 |

|   | 3.4 | Design  | n and Implementation of the PASM CNN Accelerator       | 56 |

|   | 3.5 | Evalu   | ation of PASM in a CNN accelerator                     | 60 |

|   |     | 3.5.1   | ASIC Results                                           | 60 |

|   |     | 3.5.2   | FPGA Results                                           | 63 |

|   |     | 3.5.3   | Overall Results                                        | 67 |

|   | 3.6 | Concl   | usion                                                  | 68 |

| 4 | Har | dware ( | Optimised Bit-sliced Floating-Point Operators for CNNs | 71 |

|   | 4.1 | Introd  | luction                                                | 71 |

|    | 4.2          | Background and Motivation |                                                              |       |

|----|--------------|---------------------------|--------------------------------------------------------------|-------|

|    | 4.3 Approach |                           |                                                              | 76    |

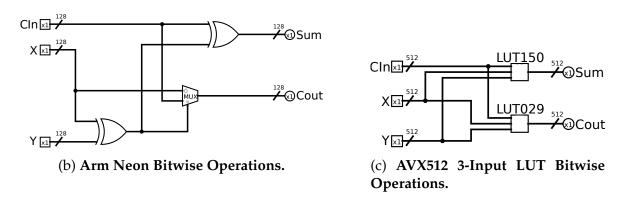

|    |              | 4.3.1                     | HOBFLOPS Cell Libraries for Arm Neon, Intel AVX2 and AVX51   | 12 7  |

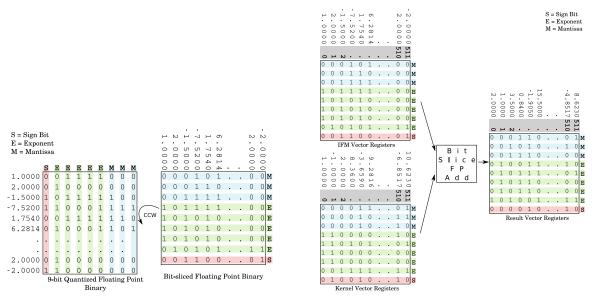

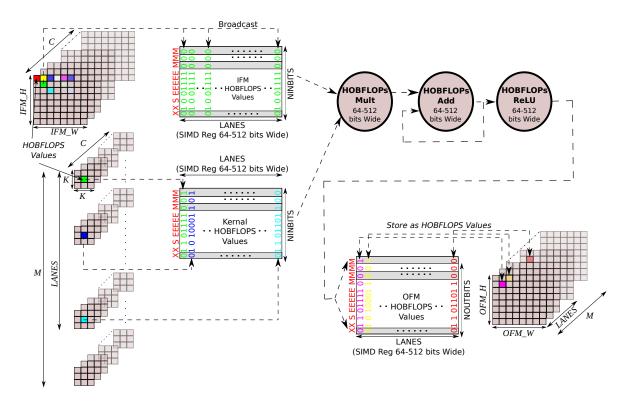

|    |              | 4.3.2                     | HOBFLOPS Bitslice Parallel Operations                        | 81    |

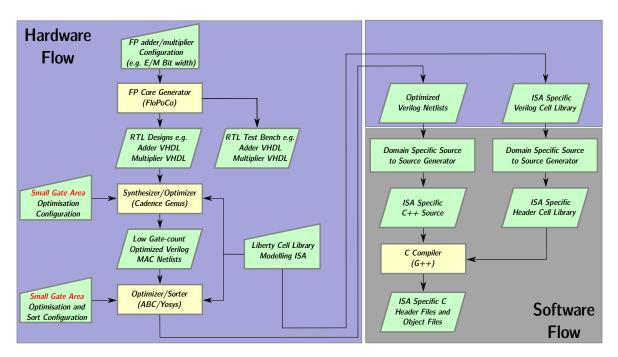

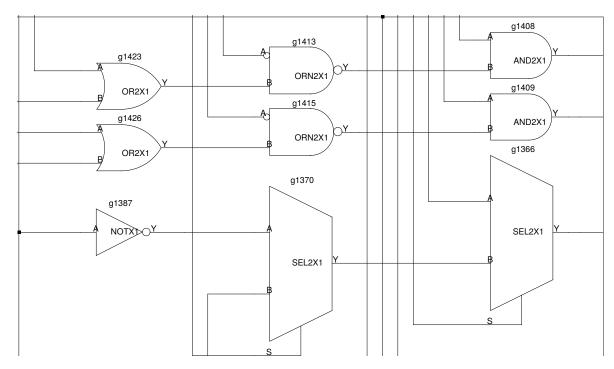

|    |              | 4.3.3                     | HOBFLOPS Design Flow                                         | 82    |

|    |              | 4.3.4                     | CNN Convolution with HOBFLOPS                                | 86    |

|    | 4.4          | Evalua                    | ation                                                        | 87    |

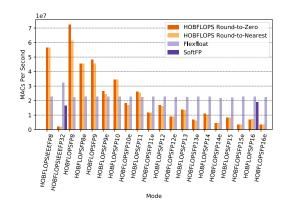

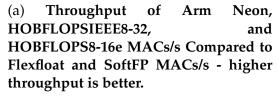

|    |              | 4.4.1                     | Arm Cortex-A15 Performance                                   | 89    |

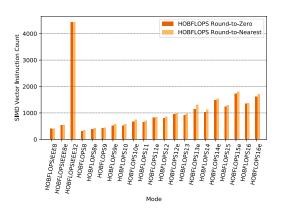

|    |              | 4.4.2                     | Intel AVX2 Performance                                       | 90    |

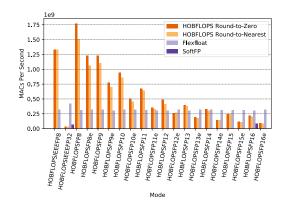

|    |              | 4.4.3                     | Intel AVX512 Performance                                     | 92    |

|    | 4.5          | Relate                    | ed Work                                                      | 93    |

|    | 4.6          | Concl                     | usion                                                        | 94    |

| 5  | Con          | clusior                   | 1                                                            | 97    |

|    | 5.1          | Contri                    | ibutions and Discoveries                                     | 97    |

|    | 5.2          | Future                    | e Directions                                                 | 99    |

|    | 5.3          | Final 7                   | Thoughts                                                     | 100   |

| Aį | peno         | dices                     |                                                              | 102   |

| A  | Neu          | ral Net                   | tworks: Background and History                               | 103   |

|    | A.1          | Introd                    | luction                                                      | 103   |

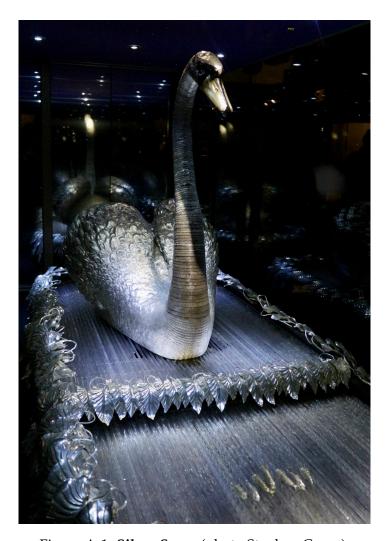

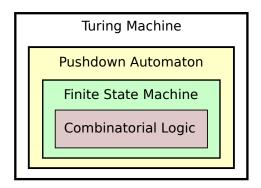

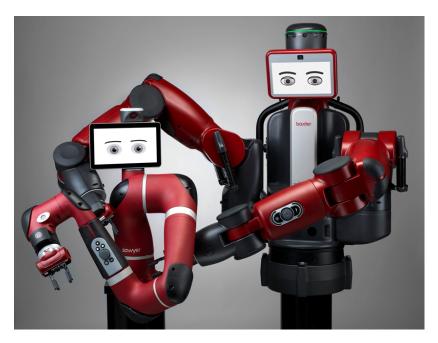

|    |              | A.1.1                     | Automata and Robotics                                        | 104   |

|    |              | A.1.2                     | Machine Learning (ML)                                        | 108   |

|    | A.2          | A Con                     | ncise History of AI                                          | 109   |

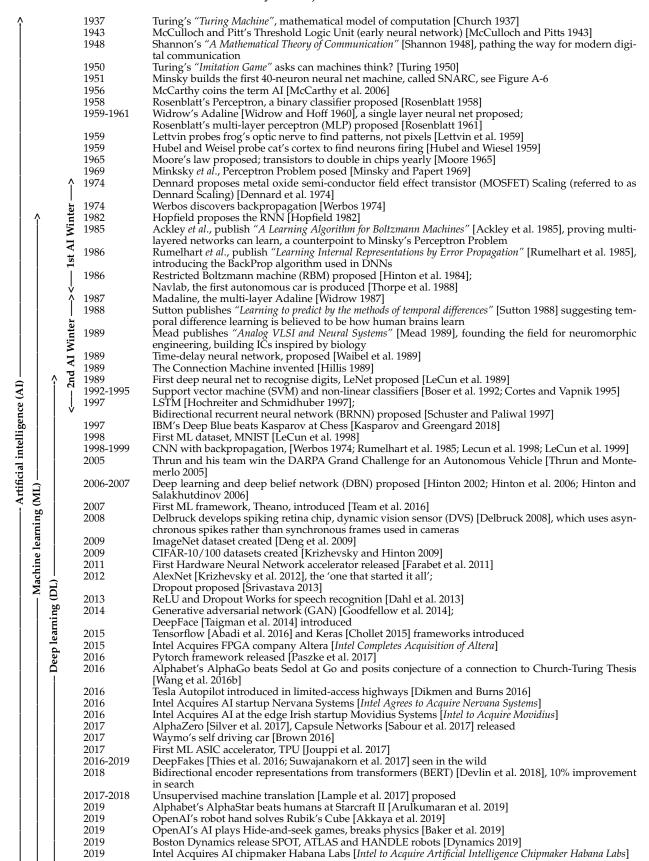

|    |              | A.2.1                     | Highlights of Early AI Discovery, Innovation and Development | t 109 |

|    |              | A.2.2                     | The Perceptron and Multi-layer Networks                      | 112   |

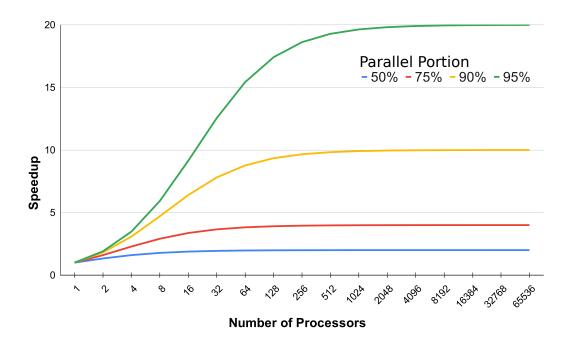

|    |              | A.2.3                     | Amdahl's Law And Its Effect on AI                            | 113   |

|    |              | A.2.4                     | The XOR Problem and the Dawn of the First AI Winter          | 114   |

|    |              | A.2.5                     | Moore's Law and Dennard's Scaling                            | 115   |

|    |              | A.2.6                     | Connection Machines                                          | 115   |

|    |              | A.2.7                     | The Second AI Winter                                         | 116   |

|    |              | A.2.8                     | The Advent of Modern-Day Vision Machine Learning             | 116   |

|    |              | <b>A 2</b> 0              | ImagaNot                                                     | 115   |

|   |       | A.2.10  | ILSVRC and Kaggle Competitions             | 118 |

|---|-------|---------|--------------------------------------------|-----|

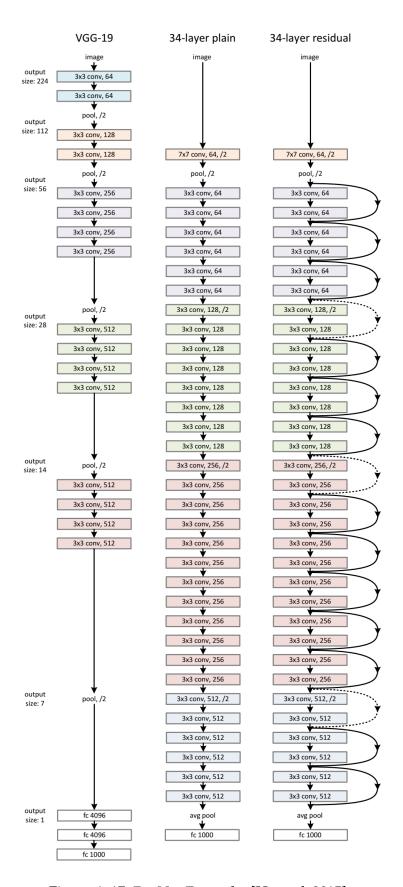

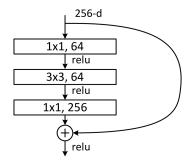

|   | A.3   | Most l  | Influential CNN Models                     | 119 |

|   | A.4   | Challe  | enges of Deep Learning                     | 125 |

|   | A.5   | Concl   | usion                                      | 127 |

| В | Intro | oductio | on to Convolutional Neural Networks (CNNs) | 129 |

|   | B.1   | Introd  | ucing Neural Networks                      | 129 |

|   | B.2   | Artific | cial Neural Networks and Machine Learning  | 129 |

|   |       | B.2.1   | Categories and Applications of ML          | 130 |

|   |       | B.2.2   | The Brain and Vision                       | 131 |

|   |       | B.2.3   | Deep Learning                              | 132 |

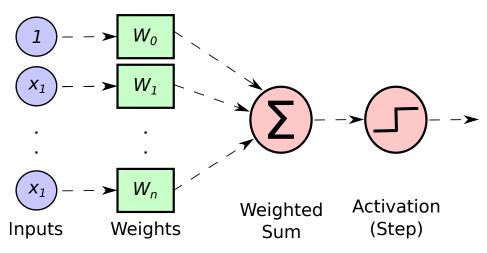

|   |       | B.2.4   | Artificial Neural Network Model            | 133 |

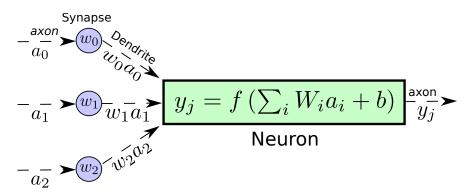

|   |       | B.2.5   | Training The Neural Network                | 137 |

|   | B.3   | Convo   | olutional Neural Networks                  | 144 |

|   |       | B.3.1   | Calculating the MAC Operations in a CNN    | 146 |

# List of Figures

| 2-1  | Architectures of LNZ Detection Node and Processing Element             | 15 |

|------|------------------------------------------------------------------------|----|

| 3-5  | PASM in Operation                                                      | 48 |

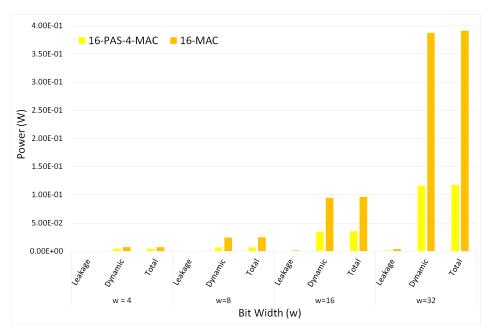

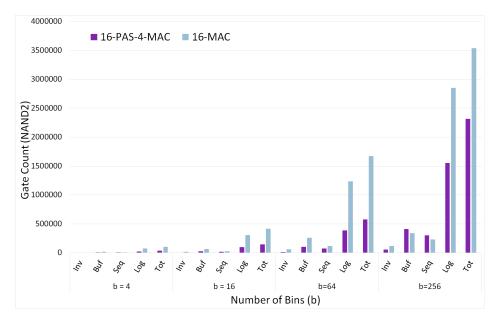

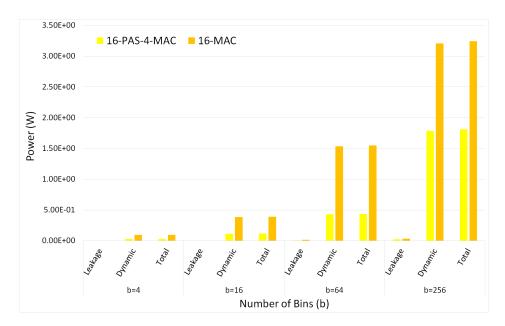

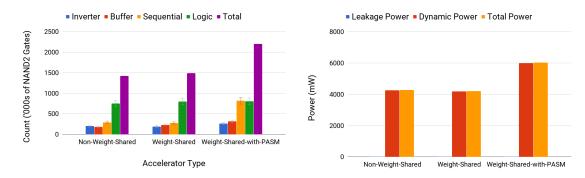

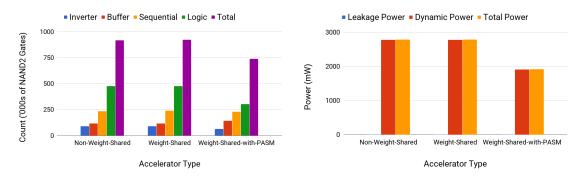

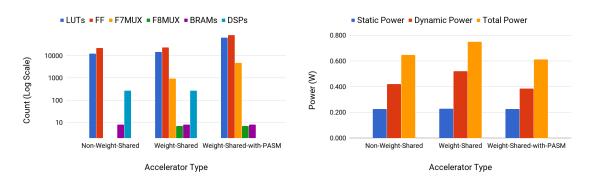

| 3-13 | 4-bin, 32-bit PASM Gate Count and Power Comparisons in ASIC            | 61 |

| 3-14 | 8-bin, 32-bit PASM Gate Count and Power Comparisons in ASIC            | 62 |

| 3-15 | 16-bin, 32-bit PASM Gate Count and Power Comparisons in ASIC           | 63 |

| 3-16 | 4-bin, INT8-bit PASM Gate Count and Power Comparisons in ASIC.         | 63 |

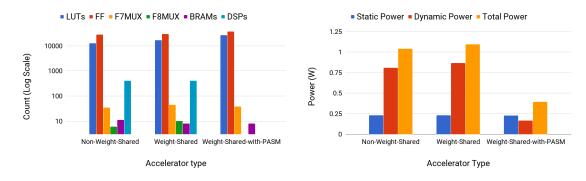

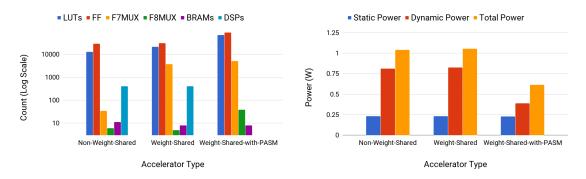

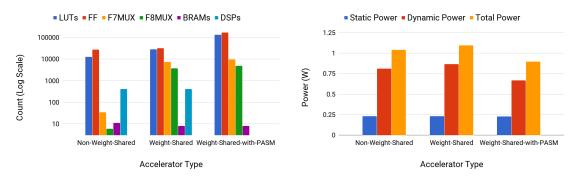

| 3-17 | 4-bin, 32-bit PASM Gate Count and Power Comparisons in FPGA            | 65 |

| 3-18 | 8-bin, 32-bit PASM Gate Count and Power Comparisons in FPGA            | 65 |

| 3-19 | 8-bit, 32-bit PASM Gate Count and Power Comparisons in FPGA            | 66 |

| 3-20 | 8-bin, INT8-bit PASM Gate Count and Power Comparisons in FPGA.         | 66 |

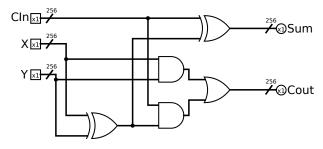

| 4-2  | Full Adders Implemented in AVX2, AVX512 and Neon                       | 80 |

| 4-3  | Bit-sliced Parallel FP Transformation and Bit-sliced FP Add Operation. | 81 |

| 4-6  | Throughput and SIMD Count of Arm Neon HOBFLOPS MACs                    | 89 |

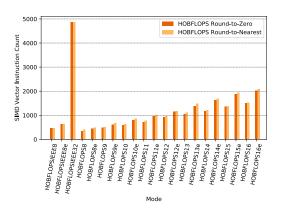

| 4-7  | Throughput and SIMD Count of Intel AVX2 HOBFLOPS MACs                  | 91 |

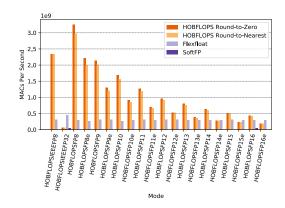

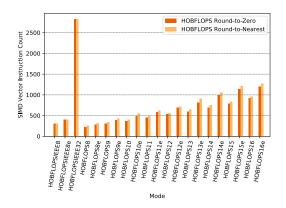

| 4-8  | Throughput and SIMD Count of Intel AVX512 HOBFLOPS MACs                | 92 |

## List of Tables

| 2.1        | Taxonomy of Related Research                                       | 10    |

|------------|--------------------------------------------------------------------|-------|

| 3.1<br>3.2 | Complexity of MAC, Weight-shared MAC and PAS                       |       |

|            | HOBFLOPS Cell Libraries' Support                                   |       |

| 4.2        | Bit Width Comparisons of Existing Custom FP                        | 82    |

| 4.3        | HOBFLOPS MAC Standard and Extended Range and Precision Types       | 82    |

| A.1        | Timeline Taxonomy of major milestones of AI, ML and DL             | 111   |

| A.2        | ILSVRC Winning CNNs                                                | 118   |

| B.1        | Number of Arithmetic Operations, Activations and Parameters in CNN | s.147 |

## **Acronyms**

**ACACES** Advanced Computer Architecture and Compilation for high-performance Embedded Systems.

**AI** artificial intelligence.

**AIG** AND-inverter graph.

ANN artificial neural network.

**ASIC** application-specific integrated circuit.

BAT Baidu, Alibaba, Tencent.

**BERT** bidirectional encoder representations from transformers.

bfloat16 brain floating point 16-bit.

BIC bit clear.

**BLAS** basic linear algebra subprograms.

**BNN** binary neural network.

**BRAM** block RAM.

**BRNN** bidirectional recurrent neural network.

**CIFAR** Canadian Institute For Advanced Research.

CNN convolutional neural network.

**CPU** central processing unit.

**CT** computed tomography.

**DBN** deep belief network.

DL deep learning.

**DARPA** Defense Advanced Research Projects Agency.

**DNN** deep neural network. **DRAM** dynamic RAM. **DSP** digital signal processor. **DVS** dynamic vision sensor. **EIE** efficient inference engine. **ELU** exponential linear unit. FC fully connected. FFT fast fourier transform. **FIFO** first in first out. **FloPoCo** FLOating-POint COres. **FLOPS** floating-point operations per second. **FP** floating-point. **FPGA** field programmable gate array. **FPS** Frame per Second. FPU floating-point unit. **FSM** finite-state machine. **GAN** generative adversarial network.

**GDPR** General Data Protection Regulation.

**GEMM** general matrix multiply.

**GFLOPS** giga floating-point operations per second (FLOPS).

**GMAFIA** Google, Microsoft, Apple, Facebook, Intel, Amazon.

**GOPS** giga operations per second.

**GPGPU** general purpose graphics processor unit (GPU).

GPU graphics processor unit.

**HDL** hardware description language.

**HiPEAC** High Performance and Embedded Architecture and Compilation.

**HLS** high-level synthesis.

**HOBFLOPS** hardware optimized bitslice-parallel floating-point operators.

IC integrated circuit.

**IET** Institution of Engineering and Technology.

**IFM** input feature map.

**ILP** instruction-level parallelism.

**ILSVRC** ImageNet large scale visual recognition challenge.

**IoT** internet of things.

**ISA** instruction set architecture.

**LSTM** long short term memory.

LUT look up table.

MAC multiply-accumulate.

**ML** machine learning.

MLP multi-layer perceptron.

MNIST Modified National Institute of Standards and Technology.

MOSFET metal oxide semi-conductor field effect transistor.

NAN not-a-number.

**NLP** natural language processing.

NN neural network.

**NPU** network processing unit.

**OFM** output feature map.

**OPS** operations per second.

**OSU** Oklahoma State University.

**PAS** parallel accumulate and store.

**PASM** parallel accumulate shared MAC.

**PE** processing element.

**PFLOPS** peta FLOPS.

PRELU parametric rectified linear unit.

**RAM** random access memory.

**RBM** restricted Boltzmann machine.

**RCNN** Region Based CNN.

**ReLU** rectified linear unit.

**RL** reinforcement learning.

**RNN** recurrent neural network.

**ROS** robot operating system.

RTL register transfer logic.

**SAT** satisfiability.

**SDC** Synopsys design constraint.

SFI Science Foundation Ireland.

**SGD** stochastic gradient descent.

**SHAVE** streaming hybrid architecture vector engine.

**SIMD** single instruction multiple data.

**SIPP** streaming image processing pipeline.

**SNARC** Stochastic Neural Analog Reinforcement Calculator.

**SOI** silicon on insulator.

**SOP** sum-of-products.

**SRAM** static RAM.

**SVE** Scalable Vector Extension.

**SVHN** street view house numbers.

**SVM** support vector machine.

**SWAR** SIMD within a register.

**TACO** Transactions on Architecture and Code Optimisation.

TFLOPS tera FLOPS.

**TOPS** tera operations per second.

TP32 tensor float 32.

**TPU** tensor processing unit.

**VLIW** very long instruction word.

**XDC** Xilinx design constraint.

YOLO You Only Look Once.

## **Glossary**

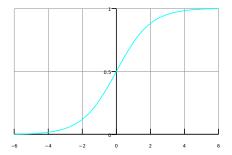

- **activation function** A function *e.g.*, sigmoid or rectified linear unit (ReLU) that takes the weighted sum of all inputs and generates a non-linear output value.

- **artificial intelligence** A program or model that can solve human-like tasks *e.g.*, language translation or image classification.

- **backpropagation** The algorithm for performing gradient descent on neural networks (NNs). The output values of each neural network (NN) layer in the graph are cached in a forward pass. The partial derivatives of the errors of a layer are calculated and used to update the weight values in a backward pass through the graph.

- **classification accuracy** The fraction of predictions that a neural network (NN) model correctly predicts.

- **convolution filter or weight** A multi-dimensional matrix having the same number of channels as the input feature map (IFM) of the convolution layer, but has a smaller height and width dimension.

- **convolution operation** Element-wise multiplication of the convolution filter and input feature map (IFM), followed by a summation of the resultant matrix values.

- **convolutional neural network** A neural network (NN) which has at least one convolution layer and also usually contains activation layers, pooling layers, fully connected layers and a classification layer.

**deep neural network** A neural network (NN) containing multiple hidden layers.

- **feedforward network** A network with connections in the forward direction only and do not cycle back.

- **gradient descent** An arithmetic means to reduce loss by calculating the gradients of loss based on model's weights, and iteratively updating the training data to minimise the loss.

- hidden layer A layer of a neural network (NN) between an input feature map (IFM) and output feature map (OFM) of a neural network (NN).

- **hyperparameter** The high abstract parameters of a neural network (NN) model that can be adjusted between training epochs to train a model, *e.g.*, learning rate.

- **inference** The process of making predictions by applying unlabelled data to a trained neural network (NN) model.

- **machine learning** An algorithm that trains a predictive neural network (NN) model from input data.

- **model** A neural network (NN) representation of a machine learning (ML) system that has been trained from a dataset.

- **neural network** A model that is composed of hidden layers consisting of connected neurons followed by some non-linearity function.

- **neuron** A node in a neural network (NN) that takes several input values and produces an output value.

- **node** A neuron in a hidden layer of a neural network (NN).

- parameter A model variable which is trained by the machine learning (ML) model.

- **precision** The number base or arithmetic bit-precision used in the convolutional neural network (CNN).

**softmax** A function that normalises the input into a probability distribution consisting of probability values proportional to the exponents of the inputs. In other words, if the numbers are a large range of positive and negative values, after applying softmax the outputs will be in the interval range (0,1) so the outputs can be interpreted as probabilities.

**sparse** The storage of non-zero values in a neural network (NN).

**uncanny valley** A hypothesised relationship between the degree an object resembles a human and a human's emotional response to such an object.

1

## Introduction

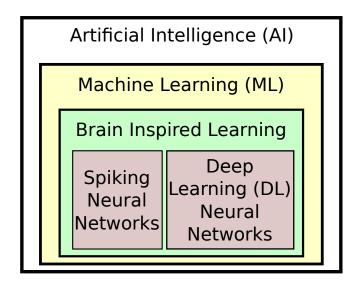

TONVOLUTIONAL NEURAL NETWORKS (CNNs) are a subset of machine learning (ML) which itself is a subset of artificial intelligence (AI). CNNs are very capable across a diverse range of vision and audio processing tasks. CNNs are excellent at classifying images [Krizhevsky et al. 2012], object detection of multiple objects within an image [Girshick et al. 2014a], real-time object detection in videos [Redmon et al. 2016] and pattern recognition in audio samples [Hershey et al. 2017]. CNNs require a large amount of storage, bandwidth, and computation of the host device on which it is implemented. For example, the CNN VGG-16 requires 154.7GMACs, and 138.36MB of parameters [Simonyan and Zisserman 2014b]. An increasing research focus is aimed at moving the CNN processing closer to 'edge' IoT devices (e.g., Han et al.'s, Deep compression work [Han et al. 2016a]) while trying to accelerate the CNN execution time and reduce energy (e.g., Howard et al.'s, MobileNets work [Howard et al. 2017]). As researchers move the models and data sets closer to implementation on edge IoT devices, they attempt to increase efficiency and reduce the size of the associated data sets. The improved efficiency will have long term impact on the environment and prevent the 'Earth glowing red-hot,' as Stephen Hawking somewhat facetiously suggested in his address to the Tencent WE Summit, in 2017.

CNNs usually operate in one of two modes:

• *training mode* where the CNN model is *trained* to detect or recognise a pattern in data, such as a human face in an image;

• *inference* mode where the model is configured to infer or *detect* the pretrained pattern in new data, *e.g.*, detect if a human face exists in a new image not yet 'seen' by the CNN model.

This work will consider optimisations of inference operation of the CNN model in embedded systems.

### 1.1 Motivation

For CNNs to operate in inference mode when implemented in embedded devices, the implementation and host device requires some or all of the following:

- Reduce the execution time and memory requirements of the CNN model while maintaining the classification accuracy;

- Hardware optimisations upon which the CNN model is to run;

- Optimise the arithmetic, numeric computation and data storage precision<sup>1</sup> of the CNN model;

- Reduce the energy consumed by the CNN on its host device.

The acceleration of CNNs is typically split into two categories; one involves accelerating the training of the CNN models; the other category is inference acceleration.

The large energy and computational requirements of CNN inference makes it challenging to implement CNNs on low-power IoT embedded devices. A contributing factor is that 90% of the computation time and energy in a CNN model is taken by the convolution unit [Farabet et al. 2010], and more specifically, the large numbers of MAC operations required. These MACs are large in integrated circuit (IC) die area, consume a large proportion of the energy, and decrease the throughput of the CNN. While some solutions manage to optimise the CNN model and its implementation enough to run successfully on a mobile device [Howard et al. 2017], this optimisation is often at the expense of throughput, performance, and classification accuracy of the model.

<sup>&</sup>lt;sup>1</sup>Note that *arithmetic precision* differs from CNN *model precision*. *Model precision* is the frequency with which a model correctly predicts a class. *Arithmetic computation and storage precision* refer to the bitwise precision of the arithmetic processing and storage medium.

## 1.2 Objective and Approach

The contributions of this thesis investigate optimising the target hardware architecture implementation of the MAC arithmetic at the heart of the CNN. We investigate a reduction in gate-level area and energy consumption in hardware and an improved execution time in both hardware and software.

These optimisation proposals are implemented for demonstration purposes in the MACs of the CNN inference on aspects and layers of the Deep Compression [Han et al. 2016a] and MobileNets [Howard et al. 2017] CNN models.

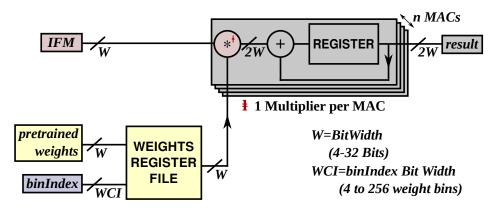

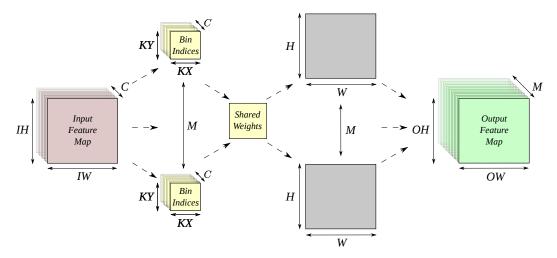

We ask if weight sharing, a novel compression scheme for weight data, could be optimised in embedded hardware to save memory, bus bandwidth and thus energy. Our work investigates the rearchitecting the MAC of a weight-shared CNN layer to discover if efficiencies in energy and ASIC die area and FPGA resources can be increased.

We also ask if bitslice optimisations of the MAC arithmetic, optimised with hardware tools, can increase throughput and performance of the MAC of the convolution layer of a CNN in software compiled for Arm and Intel CPUs.

#### 1.3 Contributions

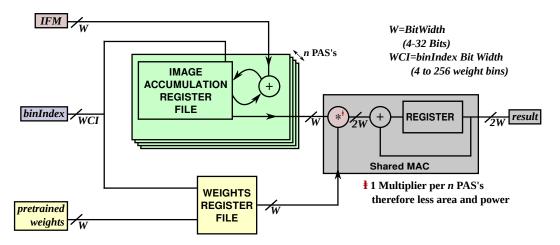

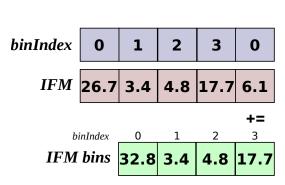

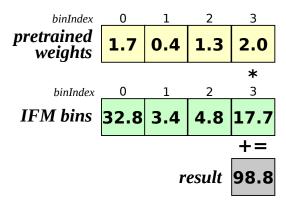

The first contribution investigates the reduction of hardware energy and IC die area while maintaining the CNNs classification accuracy in a weight-shared CNN. We call our contribution parallel accumulate shared MAC (PASM), see Chapter 3 on page 41.

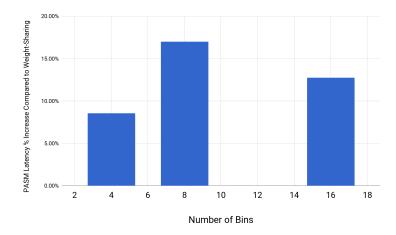

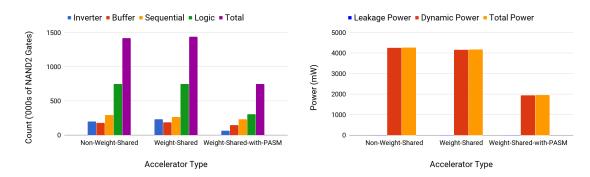

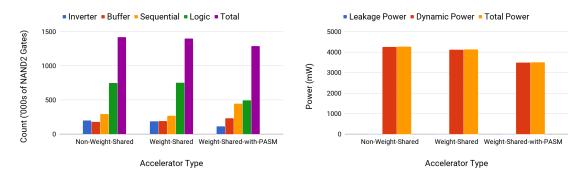

We implement PASM in a weight-shared CNN convolution hardware accelerator and analyse its effectiveness. Our experiments for a weight-shared CNN layer implemented on a 45nm ASIC process at a clock speed of 1GHz show that our approach results in 35% smaller sequential logic, 66% saving in total logic gates, and 70% less total power than the equivalent standard MAC. We also show the same weight-shared-with-PASM convolutional neural network accelerator implemented in a resource-constrained FPGA. PASM consumes 99% fewer digital signal processors (DSPs) units and 28% fewer block RAMs (BRAMs) units and consumes 18% less total FPGA reported power consumption, with up to a maximum 12% increase

in latency. Therefore, the power consumption of the convolution in an embedded system can be dialed down at the expense of an increased latency of convolution.

PASM has attracted interest from industry by Thomas Guttenberger, Founder and CEO of https://metacoder.ai/ who would like to implement PASM to reduce energy consumption.

The second contribution decreases software execution time of arbitrary-precision FP MACs contained in the convolution layer of a CNN. We exploit hardware synthesis tool optimisation and bitslicing of vector register packing and SIMD bitwise instructions for the CNN MAC. We exploit the hardware synthesiser as the C++ compiler does not perform the SIMD reduction and packing to the same efficiency. We call this contribution hardware optimized bitslice-parallel floating-point operators (HOBFLOPS), see Chapter 4 on page 71.

Our experiments show that HOBFLOPS provides a fast approach to emulating custom, low-precision FP in software. We demonstrate implementing various widths of HOBFLOPS multiplier and adder in the MAC of a CNN convolution. On Arm and Intel processors, the MAC performance in CNN convolution of HOBFLOPS, Flexfloat, and Berkeley's SoftFP are compared. HOBFLOPS outperforms Flexfloat by up to  $10\times$  on Intel AVX512. HOBFLOPS offers arbitrary-precision FP with custom range and precision, *e.g.*, HOBFLOPS9, which outperforms Flexfloat 9-bit on Arm Neon by  $7\times$ . HOBFLOPS allows researchers to prototype different levels of custom FP precision in the arithmetic of software CNN accelerators. Furthermore, HOBFLOPS fast custom-precision FP CNNs may be valuable in cases where memory bandwidth is limited.

HOBFLOPS attracted a technology journalist to interview the lead author of the work on the Youtube channel *Next Platform*.

Having introduced the research contributions, we now present the structure of this thesis.

#### 1.4 Thesis Structure

Chapter 2, analyses the state-of-the-art research in ML model implementations. We look at recent work from the late 1980s to today. We chart the key research

concepts over this period and discuss and evaluate their contributions and where they might lead the research contributions of this thesis.

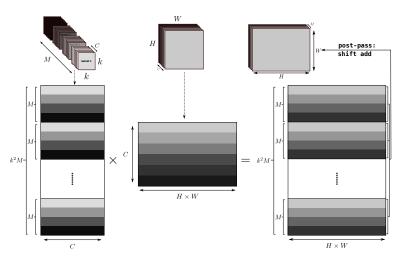

Chapter 3, presents our first contribution, which focuses on weight sharing CNNs, which we exploit to further reduce the energy dissipated by the MAC. The weightsharing compression scheme was chosen for the reduced energy dissipation from the memory access when fetching the compressed and quantised weight data. Weightsharing uses a scheme of binning compressed weight values which we exploit in our proposal. We rearchitect the MAC to replace hardware multipliers in the MAC circuit with adders and selection logic, which we call parallel accumulate shared MAC (PASM). Rather than computing the MAC arithmetic directly, which requires a large number of multipliers, we instead count the frequency of each weight and store the counts of each bin. A subsequent multiply phase computes the accumulated count value, sharing a single multiplier between multiple parallel accumulate and store (PAS) units. We significantly reduce the number of multipliers and, therefore, the IC area and energy consumption of the accelerator when implemented on ASIC. We also show that the same weight-shared-with-PASM CNN accelerator can be implemented in resource-constrained FPGAs, where the FPGA has limited numbers of DSP units to accelerate the MAC operations.

Chapter 4, presents our second main contribution, hardware optimized bitslice-parallel floating-point operators (HOBFLOPS). There is value in arbitrary and low-precision FP on both embedded and high-end devices, so this work presents a method of bitwise packing and arithmetic of FP compute while maintaining or increasing performance and reducing power consumption. Our experiments show that HOB-FLOPS provides a fast approach to emulating custom, low-precision FP in software, offering up to  $8\times$  the performance of SoftFP16. HOBFLOPS allows researchers and hardware developers to prototype different levels of custom FP precision for use in the arithmetic of CNN accelerators, the equivalent HOBFLOPS9 of which achieves up to  $6\times$  that of HOBFLOPS16. Furthermore, HOBFLOPS fast custom-precision FP CNNs in software may be valuable in cases where memory bandwidth is limited.

**Chapter 5**, discusses and evaluates the findings, suggests future work and concludes with some final thoughts for the research area.

**Appendix A**, outlines the historical background to AI. We highlight the desire for humans to automate tasks and model the physical aspects of a human to perform those tasks. We show how this desire has fuelled research and development in AI, ML and deep learning (DL), charting the major developments since World War II to present-day achievements in activities such as facial recognition, voice recognition and understanding in machines.

**Appendix B**, introduces CNNs, their properties and operation. We quickly bring the reader up to speed on CNNs and how they are trained and implemented for use in pattern recognition applications. We show some of the underlying mathematical operations that the CNN use to train for and perform the task of *e.g.*, image detection and recognition.

### 1.5 Publications

Early versions of this thesis's research appear in three refereed journal articles, one conference presentation, two poster presentations, and a co-written book chapter. At the time of writing, these works have resulted in twenty-eight citations. The PASM work has gained interest from an industry CEO. The HOBFLOPS work has garnered interest from a technology journalist.

## 1.5.1 Refereed Journals Articles

James Garland and David Gregg (2017). "Low Complexity Multiply Accumulate Unit for Weight-Sharing Convolutional Neural Networks". In: *IEEE Computer Architecture Letters* **16.2**, pp. **132–135**. ISSN: **1556-6056**. DOI: 10.1109/LCA. 2017.2656880

- Parts of this PASM work appear in chapter 3 on page 41.

- We presented a poster of this work at the 2017 High Performance and Embedded Architecture and Compilation (HiPEAC) Advanced Computer Architecture and Compilation for high-performance Embedded Systems (ACACES) summer school.

James Garland and David Gregg (2018). "Low Complexity Multiply-Accumulate Units for Convolutional Neural Networks with Weight-Sharing". In: *ACM Transactions on Architecture and Code Optimization* 15.3, 31:1–31:24. ISSN: 1544-3566. DOI: 10.1145/3233300. URL: http://doi.acm.org/10.1145/3233300

- We built significantly on the research of the initial PASM work above.

- A modified version of chapter 3 on page 41 of this thesis has been published in ACM Transactions on Architecture and Code Optimisation (TACO) journal.

- We presented the extended PASM work [Garland and Gregg 2018] at the HiPEAC 2019 conference in Valencia, Spain, on 23 JAN 2019 during paper track Session 12 Programming Models, Neural Networks<sup>2</sup>. The session Chair was Dr Luca Fanucci of the Università di Pisa<sup>3</sup>. The research was also presented at the student poster session at the same conference.

- Thomas Guttenberger, founder and CEO of https://metacoder.ai/ has expressed an interest in implemented PASM in their AI servers.

#### 1.5.2 Journal Article Submitted and Under Review

James Garland and David Gregg (2021). "HOBFLOPS for CNNs: Hardware Optimized Bitslice-Parallel Floating-Point Operations for Convolutional Neural Networks". In: PREPRINT (Version 1) available at Research Square. DOI: 10. 21203/rs.3.rs-866039/v1. URL: [https://doi.org/10.21203/rs.3.rs-866039/v1

- A modified version of chapter 4 on page 71 has been submitted for review to the Springer Soft Computing for Edge-Driven Applications journal, a preprint of which Springer store at the Research Square preprint server;

- The technology journalist, Timothy Prickett Morgan, of The Next Platform<sup>4</sup> web site and Youtube channel<sup>5</sup>, interviewed the lead author on Monday 27<sup>th</sup> July 2020 about our HOBFLOPS CNN work on their NextPlatformTV show.

## 1.5.3 Book Chapter Publications

Our initial PASM work [Garland and Gregg 2017], was published as a chapter in the 2017 HiPEAC ACACES non-peer-reviewed book.

We were invited to write a chapter to contribute to an Institution of Engineering and Technology (IET) published book in 2019.

<sup>&</sup>lt;sup>2</sup>https://www.hipeac.net/2019/valencia/#/program/paper-track

<sup>3</sup>http://www.iet.unipi.it/l.fanucci/

<sup>4</sup>https://www.nextplatform.com/

$<sup>^5</sup>$ https://www.youtube.com/channel/UC-Q65AMbMP1tGIxzSagcmHg

Andrew Anderson et al. (2019). "Hardware and software performance in deep learning". In: *Many-Core Computing: Hardware and Software*. Ed. by Geoff V. Merrett Bashir M. Al-Hashimi. Computing. Institution of Engineering and Technology. Chap. 6, pp. 141–161. ISBN: 9781785615825. DOI: 10.1049/PBPC022E. URL: https://digital-library.theiet.org/content/books/pc/pbpc022e

## 1.6 Journal Articles Peer Reviewed

During the duration of the PhD, the author of this thesis peer-reviewed the following IEEE journal articles. These works and their associated journals are very much in line with this author's research.

- *IEEE TVLSI Journal Journal:* Sungju Ryu et al. (2018). "Feedforward-Cutset-Free Pipelined Multiply–Accumulate Unit for the Machine Learning Accelerator". In: *IEEE Transactions on Very Large Scale Integration (VLSI) Systems* 27.1, pp. 138–146;

- *IEEE Access Journal Journal:* Bo Liu et al. (2019). "An Ultra-Low Power Always-On Keyword Spotting Accelerator Using Quantized Convolutional Neural Network and Voltage-Domain Analog Switching Network-Based Approximate Computing". In: *IEEE Access* 7, pp. 186456–186469;

- *IEEE Access Journal Journal:* A High-Performance Multiply-Accumulate Unit by Integrating Additions and Accumulations into Partial Product Reduction Process. C. Tung and S. Huang (2020). "A High-Performance Multiply-Accumulate Unit by Integrating Additions and Accumulations Into Partial Product Reduction Process". In: *IEEE Access* 8, pp. 87367–87377;

- *IEEE TVLSI Journal Journal:* An Energy-Efficient Asynchronous and Reconfigurable CNN Accelerator (To be published)

Here we have briefly covered from where the research motivations stem and how they have aided the development and prototyping of the research. We will now review the taxonomy of the background literature of AI to bolster the research interests.

# Taxonomy and Review of Neural Network Literature

### 2.1 Introduction

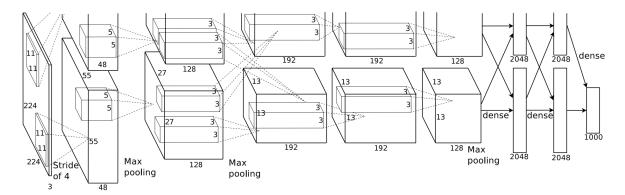

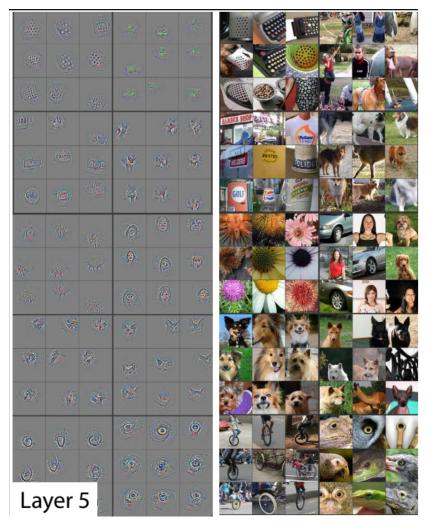

ONVOLUTIONAL NEURAL NETWORKS have become of increased interest with researchers and industry since the proposal of the AlexNet [Krizhevsky et al. 2012] deep learning (DL) neural network model. However, there are many challenges to optimising CNNs execution time, energy consumption and implementation in embedded devices, some of the challenges of which are:

- CNN Model sizes and associated training data are very large, leading to increased research in optimising the CNNs for efficient implementation and throughput in CPU, GPU, FPGA and ASIC accelerators;

- Speed of training and inference of CNNs needs to increase, but is difficult due to the large size of the CNN models and associated data;

- CNN energy efficiency needs to increase, but the large models and associated data are demanding compute and memory bandwidth that is excessive to lowpower IoT edge devices.

**Appendix A**, outlines the historical background to AI. We highlight the desire for humans to automate tasks and to model the physical aspects of a human to perform those tasks. We show how this desire has fuelled research and development in AI, ML and DL, charting the major developments since World War II to present-day achievements in activities such as facial recognition, voice recognition and understanding in machines.

Table 2.1: Taxonomy of Related Research

|                | Architecture Optimisation                                                    | Algorithm Optimisation                                                                       | Customising Bit Precision                                     |

|----------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------|

|                | FINN [Umuroglu et al. 2017] (F)                                              | AlexNet [Krizhevsky et al. 2012] (G)                                                         | FINN [Umuroglu et al. 2017] (F)                               |

| Accuracy       | Hi. Perf. FP Pipelines [De Dinechin et al.                                   | Deep Compression [Han et al. 2016a]                                                          | Hi. Perf. FP Pipelines [De Dinechin et al.                    |

|                | [ 2009] (F)                                                                  | (C,G,MG)                                                                                     | [ 2009] (F)                                                   |

|                |                                                                              | GoogleNet [Szegedy et al. 2015] (C)                                                          | Rethinking FP [Johnson 2018] (A)                              |

| Ac             |                                                                              | Granular Sparsity [Mao et al. 2017] (P)                                                      |                                                               |

|                |                                                                              | MobileNets [Howard et al. 2017] (P)                                                          |                                                               |

|                |                                                                              | ResNet [He et al. 2015] (G) VGGNet [Simonyan and Zisserman 2014b]                            |                                                               |

|                |                                                                              | (G)                                                                                          |                                                               |

|                | EIE [Han et al. 2016b] (A)                                                   | MobileNets [Howard et al. 2017] (P)                                                          | Hi. Perf. FP Pipelines [De Dinechin et al.                    |

| Area           |                                                                              |                                                                                              | 2009] (F)                                                     |

|                | Hi. Perf. FP Pipelines [De Dinechin et al.                                   | Rethinking FP [Johnson 2018] (A)                                                             | Rethinking FP [Johnson 2018] (A)                              |

|                | 2009] (F)                                                                    |                                                                                              |                                                               |

|                | Myriad 2 [Moloney et al. 2014] (A) Project Brainwave [Chung et al. 2018] (F) |                                                                                              |                                                               |

|                | Rethinking FP [Johnson 2018] (A)                                             |                                                                                              |                                                               |

|                | tensor processing unit (TPU) [Jouppi et al.                                  |                                                                                              |                                                               |

|                | 2017] (A)                                                                    |                                                                                              |                                                               |

|                | Bismo [Umuroglu et al. 2018] (F)                                             | Deep Compression [Han et al. 2016a]                                                          | EIE [Han et al. 2016b] (A)                                    |

| Energy         | D.D. M. IGI.                                                                 | (C,G,MG)                                                                                     | D. d. l. III FD F. l. 2004 S.                                 |

|                | DaDianNao [Chen et al. 2015b] (A)                                            | EIE [Han et al. 2016b] (A) Rethinking FP [Johnson 2018] (A)                                  | Rethinking FP [Johnson 2018] (A) TPU [Jouppi et al. 2017] (A) |

|                | DianNao [Chen et al. 2014] (A)  EIE [Han et al. 2016b] (A)                   | Rethinking FP [Johnson 2018] (A) Green AI [Schwartz et al. 2019] (C)                         | (A)                                                           |

|                | Eyeriss [Chen et al. 2016; Chen et al. 2019]                                 | Green in [Senward et al. 2017]                                                               |                                                               |

|                | (A)                                                                          |                                                                                              |                                                               |

|                | Myriad 2 [Moloney et al. 2014] (A)                                           |                                                                                              |                                                               |

|                | NeuFlow [Pham et al. 2012] (A)                                               |                                                                                              |                                                               |

|                | Prec'n Scalable Proc. [Moons and Verhelst                                    |                                                                                              |                                                               |

|                | 2016] (A) Rethinking FP [Johnson 2018] (A)                                   |                                                                                              |                                                               |

|                | TPU [Jouppi et al. 2017] (A)                                                 |                                                                                              |                                                               |

|                | Bismo [Umuroglu et al. 2018] (F)                                             | Backprop Handwritten Recog. [LeCun et al.                                                    | 8-bit Approximation [Dettmers 2015] (G)                       |

| Execution Time |                                                                              | 1989] (C)                                                                                    |                                                               |

|                | DaDianNao [Chen et al. 2015b] (A)                                            | BinaryConnect [Courbariaux et al. 2015a]                                                     | Bit-slice FP [Xu and Gregg 2017] (C)                          |

|                | DianNao [Chen et al. 2014] (A)                                               | (P) BinaryNet [Courbariaux et al. 2016] (G)                                                  | Deep Compression [Han et al. 2016a]                           |

|                | Billi vao [Cheff et ali 2011]                                                | Briary (Coursainance an 2010)                                                                | (C,G,MG)                                                      |

|                | Deep Learning with INT8 [Fu et al. 2016] (F)                                 |                                                                                              | Deep Learning with INT8 [Fu et al. 2016] (F)                  |

|                | EIE [Han et al. 2016b] (A)                                                   | EIE [Han et al. 2016b] (A)                                                                   | Fixed-point Quantisation [Lin et al. 2016] (P)                |

|                | FINN [Umuroglu et al. 2017] (F)                                              | Faster Int. Multiplication [Fürer 2007] (P)                                                  | Flytes [Anderson et al. 2017] (C)                             |

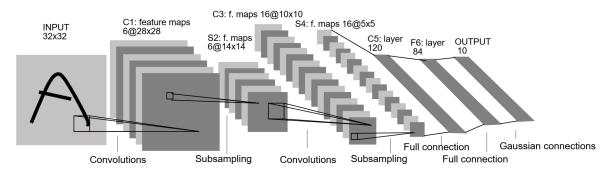

|                | Hardware Accel. CNNs [Farabet et al. 2010] (F)                               | Grad. Learn'g of Doc. Recog. [Lecun et al. 1998] (C)                                         | Hi. Perf. FP Pipelines [De Dinechin et al. 2009] (F)          |

|                | Hi. Perf. FP Pipelines [De Dinechin et al.                                   | Ltd. Numerical Precision [Gupta et al. 2015]                                                 | Ltd. Numerical Precison [Gupta et al. 2015]                   |

|                | 2009] (F)                                                                    | (F)                                                                                          | (F)                                                           |

|                | Myriad 2 [Moloney et al. 2014] (A)                                           | Opt. FPGA Accel. CNNs [Zhang et al. 2015]                                                    | MobileNets [Howard et al. 2017] (P)                           |

|                | N. El [Dl ( 1 2012]                                                          | (F)                                                                                          | D : (D : [C] (10010] (F)                                      |

|                | NeuFlow [Pham et al. 2012] (A)                                               | Opt. Loop Oper'n/Dataflow [Ma et al. 2017] (F)                                               | Project Brainwave [Chung et al. 2018] (F)                     |

|                | Opt. FPGA Accel. CNNs [Zhang et al. 2015]                                    | Parallel MCMK CNN [Vasudevan et al.                                                          | TPU [Jouppi et al. 2017] (A)                                  |

|                | (F)                                                                          | 2017] (C)                                                                                    |                                                               |

|                | Opt. Loop Oper'n/Dataflow [Ma et al. 2017]                                   | Project Brainwave [Chung et al. 2018] (F)                                                    |                                                               |

|                | (F)                                                                          | VALOR N. (ID. ) 1 201(1) (C)                                                                 |                                                               |

|                | Prec'n Scalable Proc. [Moons and Verhelst 2016] (A)                          | XNOR-Net [Rastegari et al. 2016] (C)                                                         |                                                               |

|                | Project Brainwave [Chung et al. 2018] (F)                                    |                                                                                              |                                                               |

|                | TPU [Jouppi et al. 2017] (A)                                                 |                                                                                              |                                                               |

|                | EIE [Han et al. 2016b] (A)                                                   | BinaryConnect [Courbariaux et al. 2015a]                                                     | Deep Compression [Han et al. 2016a]                           |

|                | ED DIEL                                                                      | (P)                                                                                          | (C,G,MG)                                                      |

| age            | FINN [Umuroglu et al. 2017] (F)                                              | BinaryNet [Courbariaux et al. 2016] (G) Distilling Knowledge [Hinton et al. 2015] (P)        | SqueezeNet [Iandola et al. 2016] (P)                          |

| Storage        |                                                                              | Distilling Knowledge [Hinton et al. 2015] (P) Fixed-point Quantisation [Lin et al. 2016] (P) | XNOR-Net [Rastegari et al. 2016] (C)                          |

| •              |                                                                              | SqueezeNet [Iandola et al. 2016] (P)                                                         |                                                               |

|                |                                                                              | 1 (-)                                                                                        |                                                               |

There are many ways of tackling the above challenges. This chapter will look at the current research literature and discuss how researchers are addressing these challenges. The review is organised using the taxonomy shown in Table 2.1. The hardware and software levels of abstraction are the primary axis (shown in the headings at the top) of Table 2.1.

The orthogonal axis (headings on the left of Table 2.1) consists of the major research themes of the works, ideas and techniques, focusing on optimising the target hardware, optimising the algorithm or customising the bit-precision:

- Accuracy: Research that focuses on optimising the number representation accuracy or CNN prediction accuracy;

- **Area**: How researchers optimise the utilised area of IC or memory footprint of the CNN;

- Energy: Optimising the energy dissipated within the CNN, with a focus on inference;

- Execution Time: Research proposals put forward to optimise the speed, throughput or latency of the CNN. Much focus on execution time, both within software and hardware has been the driver of a great deal of CNN research;

- **Storage**: The quantity of storage required by the CNN due to the optimisation strategies. The storage and movement of the weights and parameters data will increasingly move toward the memory elements.

In brackets after each piece of research, a letter appears in bold. These letters indicate the implementation technology which may impact the energy consumption, throughput and accuracy of the CNN:

- A means the research work implements the researcher's proposal in an ASIC;

- **F** shows the target is FPGA implementation;

- **G** implements the proposal in general purpose GPU (GPGPU);

- MG targets a mobile GPU for the proposals implementation;

- C indicates a CPU implementation;

- P suggests the technique doesn't state how the proposal is implemented; it is

presumed the contribution is implemented in software in a CPU.

We categorise the focus or investigation of each research area to determine under which primary and orthogonal axis to place the work. Entries may appear more than once where the entries support either multiple research themes or multiple levels of abstraction. The levels of abstraction form the sections of this chapter. Each research theme and implementation technology is addressed within the levels of abstraction sections.

While addressing the above challenges researchers implement various optimisation strategies, where applicable, in their hardware and software implementations. There are several ways to optimise for accuracy while focusing on execution time and energy dissipation, the popular methods of which are:

- 1. Optimise the CNN architecture *e.g.*,

- (a) Create larger deep CNN models for improved classification accuracy (see Table A.2);

- (b) Compress, prune or change the sparsity of the weight and/or input feature map (IFM) data;

- (c) Create a new layer type with few weights;

- (d) Create alternative convolution methods;

- (e) Produce a software library of functions, such as basic linear algebra subprograms (BLAS);

- 2. Optimise the number precision and operators of the CNN *e.g.*,

- (a) Reduce the precision of the number format and arithmetic used in the algebra of a CNN;

- (b) Optimise arithmetic operators;

- (c) Use other techniques such as bit slicing;

- 3. Create custom hardware accelerators *e.g.*,

- (a) Create a specific DSP vector processor;

- (b) Create specific FPGA and ASIC accelerators;

- 4. Focus specifically on energy conservation *e.g.*,

- (a) Create space and time efficient models to fit on low-power devices;

(b) Improve data efficiency by reducing data movement and reducing the overall data requirements.

We shall investigate how the works of Table 2.1 use these optimisation strategies.

## 2.2 Architecture Optimisations

The next subsections will examine the architectural optimisations of the CNN model (see column 1 of Table 2.1) mainly from an implementation perspective. However, as we will see, the optimisations of the implementation of the CNN model often go hand-in-hand with high-level model optimisations. We will highlight various sub-categories with capitalised sub-headings, corresponding to the above-itemised challenges.

## 2.2.1 Architecture Optimisation - Accuracy

Researchers strive to maintain or increase the CNN classification accuracy while optimising CNN models for the target architecture such as an FPGA.

## 2. OPTIMISE THE NUMBER PRECISION AND OPERATORS OF THE CNN: 2(a). REDUCE PRECISION OF NUMBER FORMAT AND ARITHMETIC:

A popular optimisation method is low-level reduction in precision of the number format and arithmetic performed by the CNN model. For example, reducing weights and arithmetic to their binary representations. Umuroglu *et al.*, [2016] propose FINN, a binary neural network (BNN) framework for building fast and flexible FPGA accelerators. Using the Canadian Institute For Advanced Research (CIFAR)-10 [Krizhevsky and Hinton 2009] and street view house numbers (SVHN) [Netzer et al. 2011] datasets, Umuroglu *et al.*, show 21906 image classifications per second with  $283\mu s$  latency and 80.1% and 94.9% classification accuracy respectively, the fastest classification in FPGA at the time of their publication. However, training the CNN with reduced binary representation weights is time-, compute- and energy-intensive. Figure 1 of [Courbariaux et al. 2016] shows BNNs are at least  $10 \times$  slower to train, but exhibit accuracy close to that of 32-bit float deep neural networks (DNNs).

Design of FPGA and ASIC hardware accelerators at the register transfer logic (RTL) level with reduced bitwise precision, can be laborious and prone to errors. De Dinechin *et al.'s*, [2009; 2011] propose automated methods of producing VHDL components with custom precision that can be used in CNNs. We exploit this type of automation in our HOBFLOPS proposal (section 4.1).

## 2.2.2 Architecture Optimisation - Area

Today, CNNs are often very large such as ResNet [He et al. 2015]. The model size has led researchers to optimise the overall area of the accelerator designs. Researchers often rearchitect the CNN to implement it in a DSP/vector processor or custom ASIC and FPGA based CNN accelerators.

## 2. OPTIMISE THE NUMBER PRECISION AND OPERATORS OF THE CNN: 2(a). REDUCE PRECISION OF NUMBER FORMAT AND ARITHMETIC:

Designing dedicated hardware for FPGA and ASIC allows designers to produce different number representations and data types. Alternative number representations reduce the data storage requirements, thus allowing a smaller gate-level area of accelerator design to be produced.

Johnson [2018] proposes an alternative floating-point representation and a hybrid log multiply/linear add function, Kulisch accumulation, and tapered encodings from Gustafson's posit format for accelerators. Johnson shows that a 16-bit log float multiply-add is  $0.68\times$  the IC die area compared with an IEEE-754 float16 fused multiply-add while maintaining the same significand precision and dynamic range.

Microsoft propose the alternative MS-FP8 and MS-FP8 FP representations [Chung et al. 2018], a highly quantised version of IEEE FP-754 standard, allowing tight implementation in FPGA DSP units.

#### 3. CREATE CUSTOM HARDWARE ACCELERATORS:

#### 3(a). CREATE SPECIFIC DSP/VECTOR PROCESSOR:

The streaming hybrid architecture vector engine (SHAVE) v3.0 processor in the Myriad 2 [Moloney et al. 2014] is a 128-bit SIMD 12-very long instruction word (VLIW) vector processor which can support various bit widths of integer and FP representations. Within the Myriad 2, there are 12 SHAVE processors connected to their streaming image processing pipeline (SIPP) computational imaging hardware accelerators via a crossbar. Myriad 2 employs optimised scratch pads, caches,

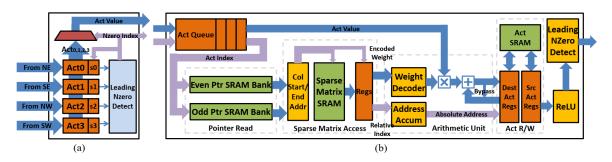

Figure 2-1: The architecture of the Leading Non-zero Detection Node (a) and architecture of Processing Element (b) [Han et al. 2016b].

instruction-level parallelism (ILP), first in first outs (FIFOs), and other queuing mechanisms. Myriad 2 produces an accelerator that has very competitive giga FLOPS (GFLOPS)/W compared with the Nvidia's Tegra K1 GPU accelerator but with a very small IC die size. Myriad 2 is often used in embedded low-power applications, such as DL vision systems on the DJI Spark and other drones [Movidius 2017].

#### 3(b). CREATE SPECIFIC FPGA and ASIC ACCLERATOR:

De Dinechin *et al.*, [2009; 2011] show that they can control the post synthesis gate-level area of both of their 32-, and 64-bit RTL accelerators with their automation mentioned above.

Han *et al.*, [2016b] evaluate a pruned and compressed (via weight-sharing) inference engine implemented in both a TSMC 45nm and 28nm CMOS process ASICs. Their efficient inference engine (EIE) hardware accelerator can store all weights in on-chip static RAM (SRAM). They show that compared with DaDianNao [Chen et al. 2015b] of Chen Y. *et al.*, EIE achieves  $3\times$  smaller area. Han *et al.*, layout a processing element (PE) and approximate the area of a PE to be  $638,024\mu$   $m^2$ . Figure 2-1 demonstrates the level of rearchitecting the CNN undergoes to reduce the area of the CNN model and associated data. Their optimisations show no loss in accuracy.

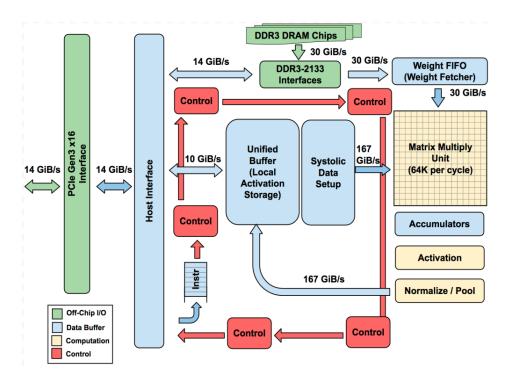

Google's TPU [Jouppi et al. 2017] area, when implemented in ASIC silicon measures around  $331mm^2$  (see Figure 2-2 for a block diagram). This compares favourably to the competing Intel Haswell CPU and Nvideo K80 GPU which are roughly double the IC die area.

## 2.2.3 Architecture Optimisation - Energy

Often researchers target FPGA and ASIC architectures as they generally dissipate lower energy than CPU or GPU implementations of the CNN accelerator.

Figure 2-2: **TPU Block Diagram** [Jouppi et al. 2017].

#### 1. OPTIMISE THE CNN ARCHITECTURE:

#### 1(b). COMPRESSION, PRUNING, SPARSITY:

Moons *et al.*, built on their Energy Efficient ConvNets work [Moons et al. 2016] to produce the Precision Scalable Processor [Moons and Verhelst 2016], a CNN ASIC that is a custom fully C-programmable processor. Their proposal applies quantisation schemes down to layer granularity, applies precision scaling to their accelerator circuits and sparsity to reduce the computations needed due to the zero-valued parameters of the precision scaling. Moons *et al.*, claim the processor consumes 25-288mW at 204 MHz.

## 2. OPTIMISE THE NUMBER PRECISION AND OPERATORS OF THE CNN: 2(a). REDUCE PRECISION OF NUMBER FORMAT AND ARITHMETIC:

Google's TPU accelerator [Jouppi et al. 2017] uses brain floating point 16-bit (bfloat16) in the systolic arrays to accelerate the matrix multiplication operations. They use 32-bit IEEE FP for accumulation and claim their TPU has a tera operations per second (TOPS)/Watt about 30X – 80X higher than that of contemporary GPUs or CPUs. As Google implement the TPU circuits in an ASIC, they intrinsically produce a lower energy CNN accelerator and claim around 40W with a peak 92TOPS, however Google does not publish exact comparisons of their energy reduction.

Bismo FPGA accelerator [Umuroglu et al. 2018] build hardware cost models of CNNs and show an energy efficiency of up to 1.4 TOPS/W on a PYNQ-Z1 board, impressive for a small, circa US \$200 consumer FPGA development board. Bismo uses BNNs so inference is performed at the meagre energy budget of the PYNQ-Z1.

Changing the FP number representation, Johnson [2018] work mentioned earlier shows that in 16 bits, their log float multiply-add is  $0.59\times$  the energy of IEEE-754 float16 fused multiply-add, in a 28nm ASIC process geometry.

#### 3. CREATE CUSTOM HARDWARE ACCELERATORS:

#### 3(a). CREATE SPECIFIC DSP/VECTOR PROCESSOR:

Independent analysis of the Myriad [Moloney et al. 2014] vector processor performance [Ionica and Gregg 2015] show that Myriad 1 exhibits a performance/watt ratio of 23.17 GFLOPS/W while Movidius claim a 500mW operation.

#### **3(b). CREATE SPECIFIC FPGA and ASIC ACCELERATOR:**

Custom accelerators are often more expensive initially to produce than vector processors but allow for reduced energy consumption, smaller devices, and cheaper mass production. Hardware can have reduced overhead of fetch/decode/execute of instructions and reduced complex pipelines with ILP, by either reducing the instruction set architecture (ISA) or removing the ISA completely and implementing a finite-state machine (FSM) in RTL. NeuFlow [Pham et al. 2012] does exactly this by implementing Farabet's NeuFlow [2011] on an IBM 45 nm silicon on insulator (SOI) process. The implementation accelerates large numbers of convolutions and matrix-to-matrix operations, thus reducing data movement due to the lower bit-representation. NeuFlow can deliver up to 320 giga operations per second (GOPS) with an average power consumption of 0.6W.

By optimising the locality and bandwidth of the required weight-data memory accesses, DianNao, [Chen et al. 2014] implements large CNNs in a 65nm process ASIC. Chen T. *et al.*, rearchitect their ASIC to perform 496 parallel 16-bit fixed-point operations, reducing the energy by  $21.08 \times$  than that of a comparable 128-bit SIMD processor core clocked at 2GHz.

Later Chen Y. et al., propose DaDianNao [2015b] which shrinks the process geometry of their ASIC accelerator to 28nm. Storage of the enormous weight data is tackled by spreading the storage of all weights across the multiple accelerator nodes'

on-chip dynamic RAM (DRAM) or SRAM, thus requiring no main memory. DaDianNao outperforms a single GPU reducing energy consumption by up to  $150.31 \times$  when using 64 nodes, taking 6.12W memory power and 15.97W total power. However, DaDianNao cannot exploit sparsity or weight sharing of the weights and activations as the exploitation would need to expand the network to dense form before an operation, which would increase energy consumption.

The pruning, compression and weight-sharing scheme of EIE [Han et al. 2016b] highlighted above, demonstrate a the compressed number of MAC operations. The optimisation achieves  $19\times$  better energy efficiency than DaDianNao.

The Eyeriss [Chen et al. 2017; Chen et al. 2019] ASIC accelerators exploit the row stationary dataflow with 168 processing elements and 16-bit fixed-point integer operations, thus reducing data movement and energy. Chen *et al.*, claim that the row stationary dataflow reconfigures the computation mapping of a given shape, maximally reusing data locally to reduce expensive data movement, such as DRAM accesses and thus increasing energy efficiency. Eyeriss 2 tiles the MAC spatially across the PEs through any of the dimensions of the layers. The layers can vary in shape and size so to deal with these differences, Eyeriss 2 uses a hierarchical mesh that adapts to these variations of kernels thus improving the computation resources to perform  $2.5\times$  more energy efficiency than the predecessor Eyeriss v1 when running MobileNets.

## 2.2.4 Architecture Optimisation - Execution Time

Different researchers report different styles of metrics, *e.g.*, frames per second or TOPS, or the researchers implement different styles of an accelerator. However, all contributions give some form of metric that often shows an improvement impacted by their architectural change or form of implementation.

## 2. OPTIMISE THE NUMBER PRECISION AND OPERATORS OF THE CNN: 2(a). REDUCE PRECISION OF NUMBER FORMAT AND ARITHMETIC:

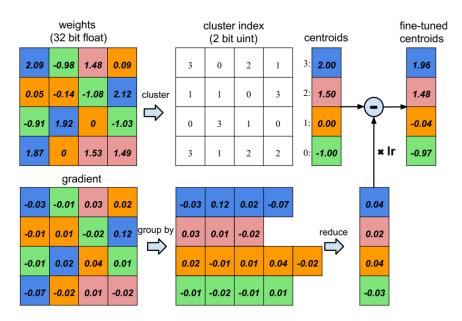

Han *et al.*, apply their deep compression optimisation techniques (see Figure 2-3) introduced above to VGG-16 CNN and find the model runs  $3 \times$  to  $4 \times$  faster on a mobile GPU with no loss in accuracy [Han et al. 2016a]. Their EIE work [Han et al. 2016b] achieves  $2.9 \times$  better throughput than DaDianNao [Chen et al. 2015b],

Figure 2-3: Weight sharing by scalar quantisation (top) and centroids fine-tuning (bottom). [Han et al. 2016a].

impressive considering EIE is implemented on the older 45nm process technology and DaDianNao is implemented on the newer, more efficient 28nm process.

Moons *et al.'s*, Precision Scalable Processor [Moons and Verhelst 2016] demonstrates yields of 0.3-2.6TOPS/W, which is  $3.9 \times$  higher than that of Eyeriss [Chen et al. 2016].

Researchers in industry often settled on an 8-bit architecture for the CNN. 8-bit architectures are less time consuming to train and implement than a BNN with most of the benefits of BNNs and most of the classification accuracy of FP accelerators. INT8 [Fu et al. 2016] changes the bit level type and precision to 8-bit integers and achieves  $1.75\times$  peak solution-level performance deep learning operations per second (OPS) compared to other FPGAs with the same resources.

Later in 2018, Microsoft's MSFP8 and MSFP9 [Chung et al. 2018] proposal mentioned above again changes the number format and datatype to their FP 8-bit and produce 720GOPS/W on an Intel Stratix 10 280.

#### 3. CREATE CUSTOM HARDWARE ACCELERATORS:

#### 3(a). CREATE SPECIFIC DSP/VECTOR PROCESSOR:

Myriad 1 [Moloney et al. 2014] has a performance of around 8.11GFLOPS, which Movidius increased to 200GFLOPS in Myriad 2, and Myriad X boasts 4 TOPS of operation.

#### 3(b). CREATE SPECIFIC FPGA and ASIC ACCELERATOR:

De Dinechin *et al.*, [2009] showcase their custom accelerator on a Xilinx Virtex-4 part, showing performance can increase from 10 cycles to 29 cycles for 32-bit FP to 10 to 46 cycles for 64-bit FP when implementing the FP Collision operator on the FPGA.

NeuFlow [Farabet et al. 2011; Pham et al. 2012] implemented on an IBM 45 nm SOI process can deliver up to 320GOPS.

Ma *et al.*, [2017] propose a CNN accelerator demonstrated on an Intel Altera Arria 10 GX 1150 FPGA. Ma *et al.*, implement a VGG-16 CNN network which achieves 645.25 GOPS of throughput and 47.97ms of latency, a  $> 3.2 \times$  enhancement compared to other FPGA implementations, and very roughly  $10 \times$  that of the accelerator of Zhang *et al.*, [2015].

Bismo FPGA accelerator [Umuroglu et al. 2018] improve upon their FINN accelerator [2017] to build hardware cost models of CNNs in a bit-serial precision and show a peak performance of 6.5TOPS on a PYNQ-Z1 board, orders of magnitude greater than the above predecessors.

Several ASIC implementations change the number representation to fixed-point.

DianNao (Figure 12 of [Chen et al. 2014]) claim that there is a minimal classification accuracy trade-off when comparing the training of Modified National Institute of Standards and Technology (MNIST) using fixed point and FP representations. 32-bit FP has an error rate of 0.0311 while 16-bit fixed-point has an error rate of 0.0337. However, the storage, bandwidth, and compute needed for fixed-point is significantly smaller than with FP. Chen *et al.*, applies tiling of their loop nest for data-locality optimisation of the convolution, pooling and classifier layers. Dian-Nao is implemented on a 65nm process ASIC and can perform 496 parallel 16-bit fixed-point operations in 1.02ns. Chen *et al.*, claim the accelerator to be  $117.87 \times 10^{-10}$  faster than the comparable 128-bit SIMD processor core clocked at 2GHz.

DaDianNao [2015b], implemented on a 28nm ASIC compared to DianNao's 65nm implementation, outperforms a single GPU by up to  $450.65 \times$  when using 64 nodes, a massive increase in performance.

The first generation of the TPU [Jouppi et al. 2017] was an 8-bit integer matrix multiplication accelerator and tended to be used in inference only. Their second-generation moved from fixed-point to FP support, so it could accelerate training

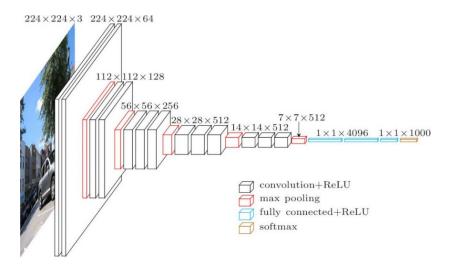

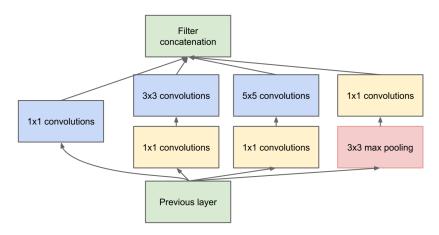

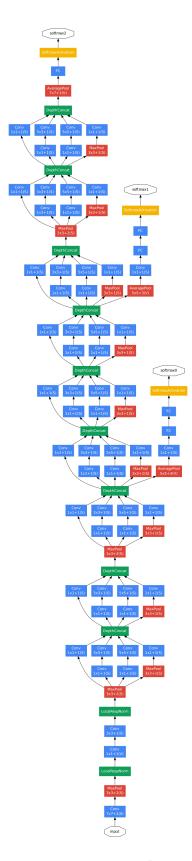

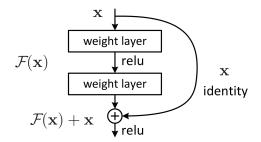

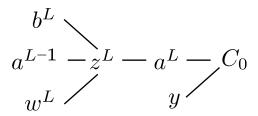

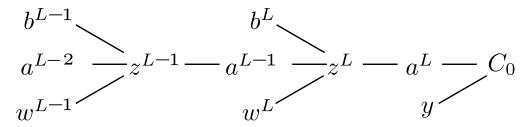

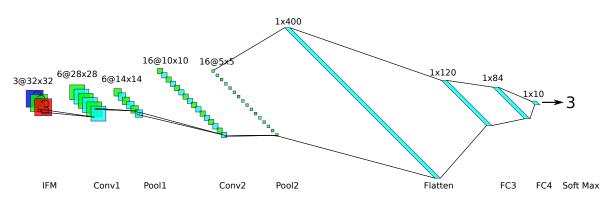

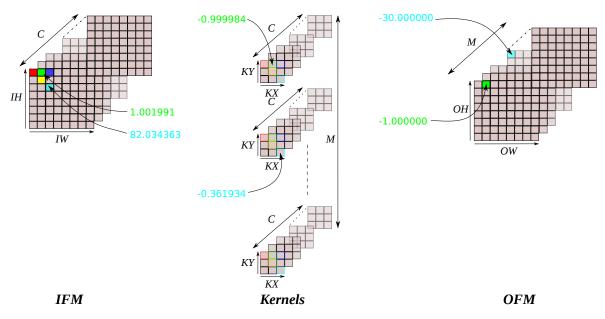

and have increased classification accuracy. Google significantly improved the memory bandwidth to 600GB/s and performance of 45tera FLOPS (TFLOPS). Google arranged the TPUs into 4-chip modules to raise the performance to 180TFLOPS. Google goes further to cascade 64 modules increasing performance to 11.5peta FLOPS (PFLOPS). Their third-generation TPU claims to be twice as powerful as the second-generation, suggesting up to 23PFLOPS of performance. Google achieve this performance by deploying the TPUs in pods with four times the number of TPU ICs as TPU 2 showing an 8-fold increase in FLOPS.