# Composition and Stress Analysis in Si/SiGe Structures

J. McCarthy, T.S. Perova, R.A. Moore,

Department of Electronic and Electrical Engineering

University of Dublin, Trinity College

Dublin 2, Ireland

Abstract — Strained Si technology enables improvements in CMOS performance and functionality via replacement of the bulk, cubic-crystal Si substrate with a Si substrate that contains a tetragonally distorted, biaxially strained Si thin film at the surface. Here we use micro-Raman spectroscopy to enable us to characterise growth processes of strained silicon, and to characterise the resulting level of strain/stress in the silicon and the effect it has on the underlying layer of graded SiGe.

### 1. INTRODUCTION

Strained silicon is an important innovation and is now an integral part of the semiconductor industry's roadmap. Strained Si technology enables improvements in CMOS performance and functionality via replacement of the bulk, cubic-crystal Si substrate with a Si substrate that contains a tetragonally distorted, biaxially strained Si thin film at the surface. Due to changes in its crystalline structure (i.e. its symmetry is different due to its strain state), the strained Si film has electronic properties that are superior to those of bulk Si. Specifically, the strained Si film has greater electron and hole mobilities, which translate into greater drive current capabilities for NMOS and PMOS transistors, respectively. This increased transistor drive current can be traded off for a reduction of dynamic power consumption.

When a thin layer of Si is grown on relaxed SiGe, the resulting type-II band offset forms a well for electrons. Additionally, the biaxial tensile strain in the Si layer splits the six fold degeneracy of the conduction band, lowering the two perpendicular valleys in energy relative to the four – in place valleys. Electrons confined to these two lower energy valleys experience both a reduction in in-phonon scattering, increasing their mobility. Increased performance has also been observed in deep submicron strained Si-n MOSFETs, demonstrating the benefits of these structures at high electric fields. Biaxial tensile strain also splits the degeneracy of the valence band in Si, enabling the fabrication of enhanced mobility surface channel strained Si p-MOSFETs.

Enhanced carrier mobilities allow strained Si MOSFETs to exhibit vastly increased performance over their bulk counterparts at identical gate lengths. These performance gains are independent of traditional Si MOSFET scaling laws and device geometries. Buried channel devices generally have higher low-field mobilities and lower noise characteristics, making them suitable for high frequency applications. Electron mobility in NMOS devices saturates at Ge content of 20% and hole mobility saturates in PMOS devices at Ge content of 40%.

For high electric field applications like state of the art CMOS, the improved scalability and increased high field S. Bhattacharya, H.S. Gamble, B.M. Armstrong School of Electrical and Electronic Engineering Queen's University Belfast, UK

mobility enhancement of the surface channel strained Si device allow it to excel. The ability to tailor the performance of strained Si technology for each specific application will have a far-reaching impact, from high-speed products like microprocessors and field-programmable gate arrays, to the low-power products used in wireless communications and other mobile devices.

Therefore the technological task is to grow relaxed SiGe layer with reasonably high Ge content (x) and then to grow a strained Si layer on the top. It is well known that due to the lattice mismatch between Si and Ge ( $\sim$  4%), SiGe layer grown on Si without special conditions is always strained. There are mainly two possibilities to grow a relaxed SiGe layer, i) to grow a graded SiGe layer with gradual increase of the Ge content [1] or ii) to use a point defect introduction at the low-temperature stage of the layer growth [2]. In this work we use former technique for relaxed SiGe layer growth with Ge content of  $\sim$  20%. Micro-Raman spectroscopy has been used for composition and stress analysis in SiGe and strained Si layers in order to establish a proper process conditions for strained Si layer growth using LPCVD.

### II, EXPERIMENT

# A. Sample preparations

Epitaxial layers of strained Si were deposited on lattice-relaxed SiGe buffer layers grown on Si substrate using low pressure chemical vapour deposition (LPCVD) technique at temperature of 800°C. A compositional grading of the order of 1%μm<sup>-1</sup> or less with final Ge concentrations of about 20% used in order to obtain a low density of threading dislocations. Five samples (S1, S2, S3, S6 and S11) were prepared, using different deposition conditions. Samples S1, S2, S3 were grown on (111) oriented Cinnati Epi 4-inch p-type Si wafers with an 2-3 μm n-type epitaxial Si layer. Samples S6 and S11 were fabricated on n-type (100) oriented 4-inch Si from OKMETIC.

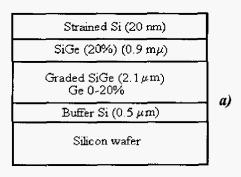

Samples S1, S2, and S3 have the same structure of deposited layers and thickness suitable for a strained-Si MOSFET as shown in Fig. 1 a. The only difference between these three samples is the structure of the graded SiGe layer (the third layer from the top) which is typically of 2.1 µm thick. S1 has a step graded layer, S2 has a linearly graded layer and S3 has a layer that is in between step and linearly graded. Relaxed, constant-composition 0.9 µm SiGe layers were grown on top of the graded layer. All layers were deposited at 800°C using silane and germane gases by LPCVD. There was no other subsequent treatment such as annealing or doping of these layers. The thickness of each layer has been estimated from the growth rate of the LPCVD process.

The processing conditions for samples S6 and S11 are given below. Si wafers were heated in nitrogen flow of 1.9x10<sup>3</sup> cm<sup>3</sup>/min at chamber pressure of 0.75 mbar until set temperature was reached. Then nitrogen was switched off, immediately SiH4 was switched on and timer was started. It took 10-12 seconds for process pressure to stabilize. All wafers were processed within 30-35 minutes of HF passivation. The following process parameters has been used (see also Table 1): temperature = 800 °C, SiH<sub>4</sub> flow -100 cm<sup>3</sup>/min, GeH<sub>4</sub> flow - 1 - 10 cm<sup>3</sup>/ min, process pressure - 0.1125 mbar with SiH<sub>4</sub> flow of 100 cm<sup>3</sup>/min, increases to maximum of 0.12 mbar with GeH<sub>4</sub> flow of 10 cm<sup>3</sup>/min. The SiGe graded layer of samples S6 and S11 are step and linearly graded, respectively, with layer structure shown in Fig. 1 b and process conditions listed in Table 1. The samples for Raman investigations with size of 10x10 mm<sup>2</sup> were cut manually from 4-inch wafers.

Figure 1. The schematic of the layers structure for samples S1, S2, S3 (a) and S6, S11 (b).

#### **B.** Raman Measurements

Raman spectra were registered in backscattering geometry using a RENISHAW 1000 micro-Raman system equipped with a Leica microscope. To prevent sample heating the power density was kept below  $10^5~\rm W/cm^2$ . The measurements were performed at room temperature with 514.5 nm line of an Ar<sup>+</sup> laser. An 1800 lines/mm grating was used in all measurements, which corresponds to a spectral resolution of  $\sim 2.5~\rm cm^{-1}$  per 3 pixels. The 100 times magnifying objectives of the Leica microscope focuses the

beam into spot of about 1 micrometer in diameter. In order to define the position of the phonon lines with a higher accuracy, the spectral lines, used for the analysis, were fitted with Lorentzian or Gaussian functions.

TABLE I GROWTH CONDITIONS FOR SAMPLES S6 AND S11

| Sample | Chamber in pressu    | base Deposition time ure, mbar (min/sec)                                                          |

|--------|----------------------|---------------------------------------------------------------------------------------------------|

| S6     | 1.7x10 <sup>-7</sup> | 3 min buffer Si, 28 min 30 sec graded<br>SiGe (10 steps), 10 min SiGe (20%)<br>10 sec strained Si |

| S11    | 3.6x10 <sup>-7</sup> | As above but with 60 steps in the graded layer region                                             |

#### III. RESULTS AND DISCUSSIONS

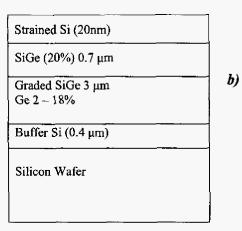

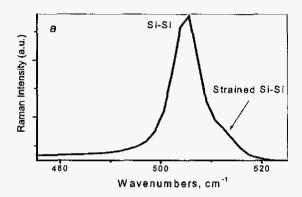

The Raman spectrum of crystalline Si has a characteristic peak at 520cm<sup>-1</sup> which corresponds to longitudinal optical (LO) phonon vibrations of the Si-Si bond. In SiGe layer this Si-Si peak will be shifted to the low-frequency side, as demonstrated in Fig. 2 (see peak at 500 cm<sup>-1</sup>), depending on Ge content (x) and stress in the layer. Other groups of phonon modes observed in Raman spectrum in the range of 450-400cm<sup>-1</sup> and 240-300cm<sup>-1</sup> are associated with SiGe layer and belong to the Si-Ge and Ge-Ge stretching modes respectively [3-6]. With strained Si deposited onto a SiGe layer, we expect all these peaks to be present in the spectrum, as well as a peak indicating the presence of strained Si.

The presence of Si-Si peak associated with Si substrate (or Si buffer layer) will depend on how deeply the laser probe beam will penetrate to the sample during Raman measurements. This will depends on the absorption coefficient ( $\alpha$ ) of the material at the wavelength of the exciting laser line and can be done by using a simple expressions for the depth of penetration ( $d_p$ ) for pure Si and Ge [7]

$$d_p = 2.3/2\alpha \tag{1}$$

and for SiGe layer

$$d_p(Si_{1-x}Ge_x) = (1-x)d_p(Si_{1-x}) + xd_p(Ge_x).$$

(2)

Using  $\alpha_{\rm si}=15080{\rm cm}^{-1}$  and  $\alpha_{\rm Ge}=600000{\rm cm}^{-1}$  at  $\lambda=514.5$  nm, we estimate  $d_p({\rm Si})\approx 763{\rm nm}$  and  $d_p({\rm Ge})\approx 19.2{\rm nm}$ . For SiGe layer with x=20%, the depth of penetration is estimated as  $d_p({\rm Si}_{0.7}{\rm Ge}_{0.2})\approx 614{\rm nm}$  using equation (2). Since the thickness of SiGe layers (constant-composition and graded one) is much higher than 614 nm, we can expect that no Si-

Si mode associated with buffer Si layer can be expected in Raman spectrum of all samples shown in Fig. 1.

The exact position of all aforementioned peaks depends on stress (for pure Si) and on stress and Ge content (for SiGe layer). It is well known that the LO peak of Si at 520cm<sup>-1</sup> will shift to the low frequency side when sample is under tensile stress and to the high frequency side under compressive stress. Fig.2 shows a Raman spectrum obtained for sample S6. The strong peak observed at 505cm<sup>-1</sup> belongs to the Si-Si mode in SiGe layer. The shoulder observed at the high frequency side of this peak belongs to a Si-Si mode in the strained Si layer. Its intensity is much lower than that for the Si-Si peak observed at 505cm<sup>-1</sup>, due to the fact that the strained silicon layer is only 20nm thick. Therefore, the most of the Raman signal originates from the SiGe layer.

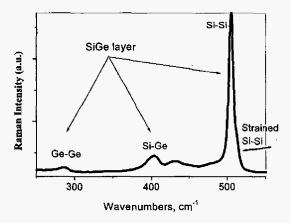

Raman spectra for samples S1, S2 and S3 are shown in Fig. 3 in the range of Si-Si modes of both layers (SiGe and strained Si). Surprisingly Si-Si peak with low intensity, which must belong to Si cap layer, appeared at frequency of 520 cm<sup>-1</sup>. This indicate the absence of any type of strain in Si cap layer. Stress relaxation of the SiGe layer was estimated at 92%, using the equation [8-10]:

$$r = (\Delta \exp - \Delta s)/(\Delta r - \Delta s)$$

(3)

where  $\Delta_{exp}$  is the measured shift of the Si-Si in the epilayer compared to that of the substrate and  $\Delta_r = 69.0x$  and  $\Delta_s = 36.0x$  for fully relaxed and fully strained layers respectively.

Fig.2 Raman intensity versus wavenumber for strained Si on SiGe layer (sample S6).

Based on these results we can conclude that the process conditions during fabrications of samples S1, S2 and S3 were not satisfactory. One of the important conditions for growing of strained Si is the absence of the threading dislocations in underlying SiGe layer. Our Raman results suggest that this condition was not fulfilled during samples fabrication. In order to confirm this suggestion all three samples were analysed using transmission electron

microscopy (TEM) and atomic force microscopy (AFM). Cross sectional TEM images are shown in Figs. 4 a and b which demonstrate characteristic cross-hatch pattern and defects respectively, from the strain field variations associated with the buried dislocations in the graded SiGe buffer layer. Short cross-hatch lines and poor morphology are observed for the relaxed-SiGe as well. The cross-hatch surface morphology arises from lateral non-uniformities in the strain field of the misfit dislocations.

Fig.3 Raman spectra of samples S1, S2 and S3 in the range of Si-Si phonon modes.

Fig. 4. Side view showing TEM micrograph of threading dislocations in SiGe layer (a) and in overall structure (b).

AFM was used to determine the threading dislocation defects densities. AFM image of the strained Si surface on the linearly-graded Si<sub>0.8</sub>Ge<sub>0.2</sub> layer grown at 800 °C is shown in Fig.5. This image shows not only that the amplitude of the roughness is relatively large, but also that the surface is faceted. Thus, Raman spectroscopy allows us to characterise the process and to predict indirectly the nature of surface topology and the presence of defects/threaded dislocations.

Fig. 5. AFM micrographs of strained Si on relaxed-SiGe layers grown on a Si wafer, from samples S1, S2, S3

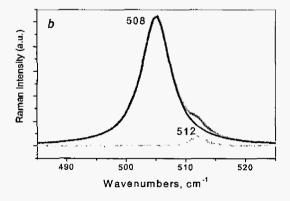

Fig 6. Raman spectrum of samples S6 (a) and S11(b) after the curve-fitting.

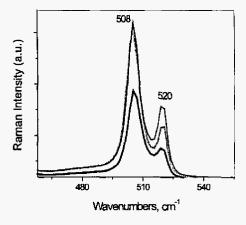

Now we are going to discuss how the Ge content in SiGe layer and the magnitude of stress in strained Si layer can be obtained. Fig. 6 a and b show Raman spectra of samples S6 and S11 in more details in Si-Si modes region. As we can see from these figures, Si-Si band for strained Si appears only as a shoulder on the more intense Si-Si band of SiGe

layer due to the overlapping of these two bands. Therefore we need to perform a band fitting in order to determine the peak positions with high accuracy, which is necessary for calculations.

Fig. 6 b shows the components in Raman spectrum of samples S11 obtained during the curve fitting with two Lorentzian functions. The curve for the strained Si layer is now can be clearly seen with peak position at ~512cm<sup>-1</sup>. The peak at 508 cm<sup>-1</sup> belongs to Si-Si band in SiGe layer. Using these peak position as well as peak positions of Si-Ge and Ge-Ge bands the magnitude of stress in strained Si layer and in SiGe layer together with Ge content can be determined using the equations discussed below.

Figure 7. TEM images of samples S6 (a) and S11 (b).

As was shown in [9] by measuring the experimental position of the three phonon lines  $(\omega_i(x))$ , the Ge content (x) and strain  $(\varepsilon)$  in SiGe layer can be determined by combination of any pair of the following three equations

$$\omega(x) = 520.0 - 68x - 830\varepsilon$$

(4)

$$\omega_{sr}(\mathbf{x}) = 400.5 + 12\mathbf{x} - 575\varepsilon \tag{5}$$

$$\omega_{xx}(x) = 282.5 + 16x - 348\varepsilon$$

(6)

However, Tsang et al. [9] have emphasised that the determination of the position of Ge-Ge band is not quite accurate for Ge content up-to  $\sim$ 50%, so only equations (4) and (5) were used to solve for Ge content and levels of strain present. For calculations of the magnitude of stress ( $\sigma$ ) present in the strained Si layer the following equation has been used [11]

$$\sigma = \left(\frac{\Delta\omega}{2x10^{-9}}\right) \tag{7}$$

where  $\Delta\omega$  is the shift of the Raman peak from unstressed Si-Si peak position at 520 cm<sup>-1</sup>. For sample S6, strained Si peak is located at 513.3cm<sup>-1</sup>, therefore the magnitude of stress was found to be  $3.31 \times 10^9$  Pa. For sample S11, made under similar conditions, strained Si peak is at 512.7cm<sup>-1</sup>, which lead to the stress magnitude of  $3.65 \times 10^9$ . For sample S6, the Ge content in SiGe constant composition layer is

21.27%, while for S11 x=22.2%. Thus, the increasing of Ge content increases strain in strained Si cap layer. This correlate with reported values for NMOSFETs which has increased electron mobility, and therefore the increased drive current, up-to a saturation at Ge content of 20%, i.e. current increases in strained Si devices up to x=20% at which point it saturates. There is no great difference in using step or linearly grown devices as our results show.

Our Raman data are in a good agreement with the results of TEM measurements for samples S11 and S6. This is demonstrated by the defect-free TEM images shown in Fig 7.

#### III. CONCLUSION

Micro-Raman spectroscopy is a fast and non-destructive tool for characterisation of strained silicon. It can be used to identify the problems with the process conditions used and predict the presence of dislocations and surface roughness. This paper shows the use and benefits of micro-Raman spectroscopy as it allows us to fine-tune our process. From micro-Raman analysis of samples S1, S2 and S3, it was obvious that the process had to be adjusted, thus acting as a feedback loop for the preparation of strained Si. By changing wafers and orientation as well as the deposited thickness of layers we managed to deposit strained Si cap layer on a relaxed SiGe layer, as was confirmed by Raman measurements for samples S6 and S11. For the latter samples we show that there is little difference in the resulting stress magnitude of Si cap layer whether we use a linear or step graded SiGe structure. Using well established equations we can also calculate Ge content and its associated strain in underlying SiGe layer.

## IV. ACKNOWLEDGEMENTS

The financial support towards this work from HEA Ireland (PRTLI Grant) is greatly acknowledged.

## V. REFERENCES

- [1] E.A. Fitzgerald, M.T. Currie, S.B. Samavedam et al, *Physica Status Solidi (a)*, vol. 171, 1999, pp. 227-238.

- [2] E. Kasper, K. Lyutovich, M. Bauer, M. Oehme, *Thin Solid Films*, vol. 336, 1998, pp.319-324.

- [4] M.A.Renucci, J.B.Renucci, and M.Kardona, in Light Scattering in Solids, edited by M.Balkanski (Flammarion, Paris, 1971), p326.

- [3] G.M. Zinger, I.P. Ipatova, and A.V. Subashiev, Fiz. Tekh. Poluprovodn. vol. 11, 1977, pp. 656-662. (Sov. Phys. Semicond. Vol. 11, 1977, pp. 383-387).

- [5] M.I.Alonso and K.Winer, *Phys.Rev.*, vol. B39, 1989, pp. 10056-10062.

- [6] D.J.Lockwood, J.M. Baribeau, *Phys. Rev.*, vol. B45, 1992, pp. 8565-8571.

- [7] Raman and Luminescence Spectroscopy for Microelectronics, p16, European Commission.

- [8] C.H.Perry, F.Lu and F.Namavar, *Solid State Commun.*, vol. 88, 1993, pp. 613-617.

- [9] J.C.Tsang, P.M. Mooney, F.Dacol, J.O.Chu, J.Appl Phys., vol. 75, 1994, pp. 8098-8108.

- [10] B.Dietrich, E.Bugiel, J.Klatt, et al., J.Appl. Phys., vol. 74, 1993, pp. 3177-3180.

- [11]. Th. Englert, G. Abstreiter, J. Pontchara, Solid-State Electron., vol. 23, 1980, 31-38.